Fifo reset setting register – FUJITSU MB86617A User Manual

Page 66

LSI S pecification

MB86617A

Rev.1.0

Fujitsu VLSI

61

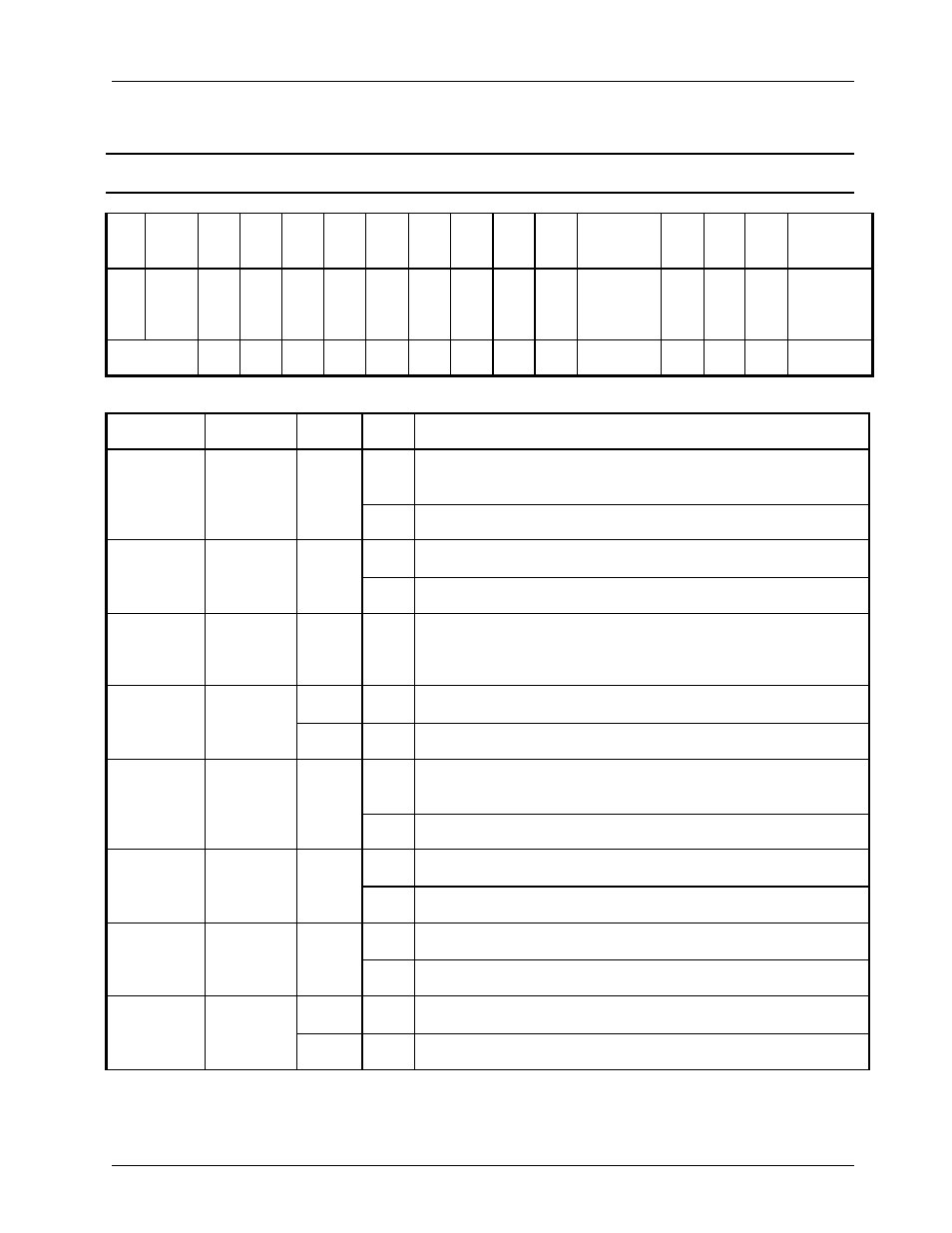

7.27. FIFO Reset Setting Register

FIFO reset setting register sets force reset of bridge and each FIFO.

AD

R/W

Bit

15

Bit

14

Bit

13

Bit

12

Bit

11

Bit

10

Bit

9

Bit

8

Bit

7

Bit

6

Bit

5

Bit

4

Bit

3

Bit

2

Bit

1

Bit

0

4Ch

R/W

reset-B

resetT

SP

FIFO-

B

reset

BRG

FIFO-

B

-

-

-

-

-

reset-

A

reset

TSP

FIFO-

A

reset

BRG

FIFO-

A

-

-

-

-

-

Initial Value

‘0’

‘0’

‘0’

‘0’

‘0’

‘0’

‘0’

‘0’

‘0’

‘0’

‘0’

‘0’

‘0’

‘0’

‘0’

‘0’

BIT

Bit Name

Action

Value

Function

0

Releases forced reset of bridge-Bch.

15

reset-B

Read/

Write

1

Executes forced reset of bridge-Bch.

0

Releases FIFO reset on TSP -IC I/F side of bridge-Bch.

14

reset TSP

FIFO-B

Read/

Write

1

Resets FIFO on TSP-IC I/F side of bridge-Bch.

0

Releases FIFO reset on LINK-I/F side of bridge-Bch.

13

reset BRG

FIFO-B

Read/

Write

1

Resets FIFO on LINK I/F side of bridge-Bch.

Read

-

Always indicate ‘0’.

12 - 8

reserved

Write

-

Always write in ‘0’.

0

Releases forced reset of bridge-Ach.

7

reset-A

Read/

Write

1

Execute forced reset of bridge-Ach.

0

Releases FIFO reset on TSP -IC I/F side of bridge-Ach.

6

reset TSP

FIFO-A

Read/

Write

1

Resets FIFO on TSP-IC I/F of bridge-Ach.

0

Releases FIFO reset on LINK-I/F side of bridge-Ach.

5

reset BRG

FIFO-A

Read/

Write

1

Resets FIFO on LINK I/F side of bridge-Ach.

Read

-

Always indicate ‘0’.

4 - 0

Reserved

Write

-

Always write in ‘0’.

Note 1) This register is not cleared automatically.

After writing ‘1’, check the state and then write ‘0’.

Note 2) Do not set ‘1’ to this register during transmit/receive execution.