FUJITSU MB86617A User Manual

Page 123

LSI S pecification

MB86617A

Rev.1.0

Fujitsu VLSI

118

11.2.2

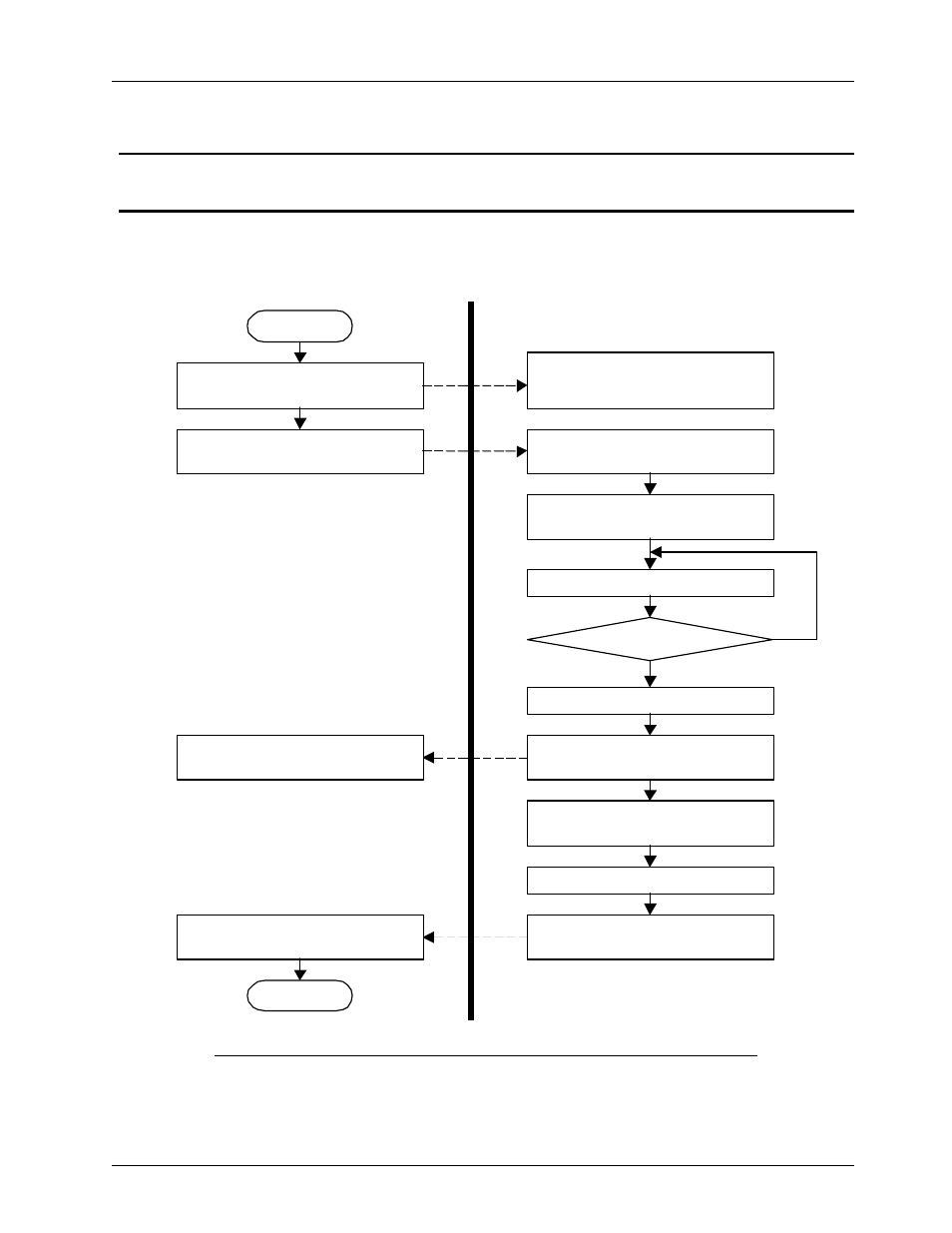

Self-ID Packet Receive after Transmitting Ping Packet Ping

Regardless of s-ID store bit setting in the mode-control register (refer to 7.1), the device receives self-ID packet after a ping

packet transmitted and stores the data removing logical inverse section in the Asynchronous receive-FIFO.

<

< Flow chart from transmitting of Pig packet to receiving Self-ID packet Ping

Figure 11.2.2.1 Flow example of operation from Pin packet transmitting to Self -ID packet receiving

START

Issue Send PHY packet(21h)

Issue instruction.

Receive Transmit PHY packet (21h)

instruction.

Read Asynchronous transmit buffer.

Transmit Ping packet.

Arbitration result

Report Physical packet send interrupt (INT25)

(assert XINT).

Store received Self-ID packet in

Asynchronous receive buffer.

Arbitration procedure

END

Read Physical packet send interrupt

(INT25)

.

Lost

Won

Store ping packet to be transmitted in

Asynchronous receive buffer.

Store pin packet (two word) to be

transmitted in Asynchronous transmit

buffer.

Report Self-ID packet received

interrupt(INT29) (assert XINT)

(XINT

)

Read Self-ID packet received interrupt

(INT29)

.

recv busy=1