Flag & status register – FUJITSU MB86617A User Manual

Page 34

LSI S pecification

MB86617A

Rev.1.0

Fujitsu VLSI

29

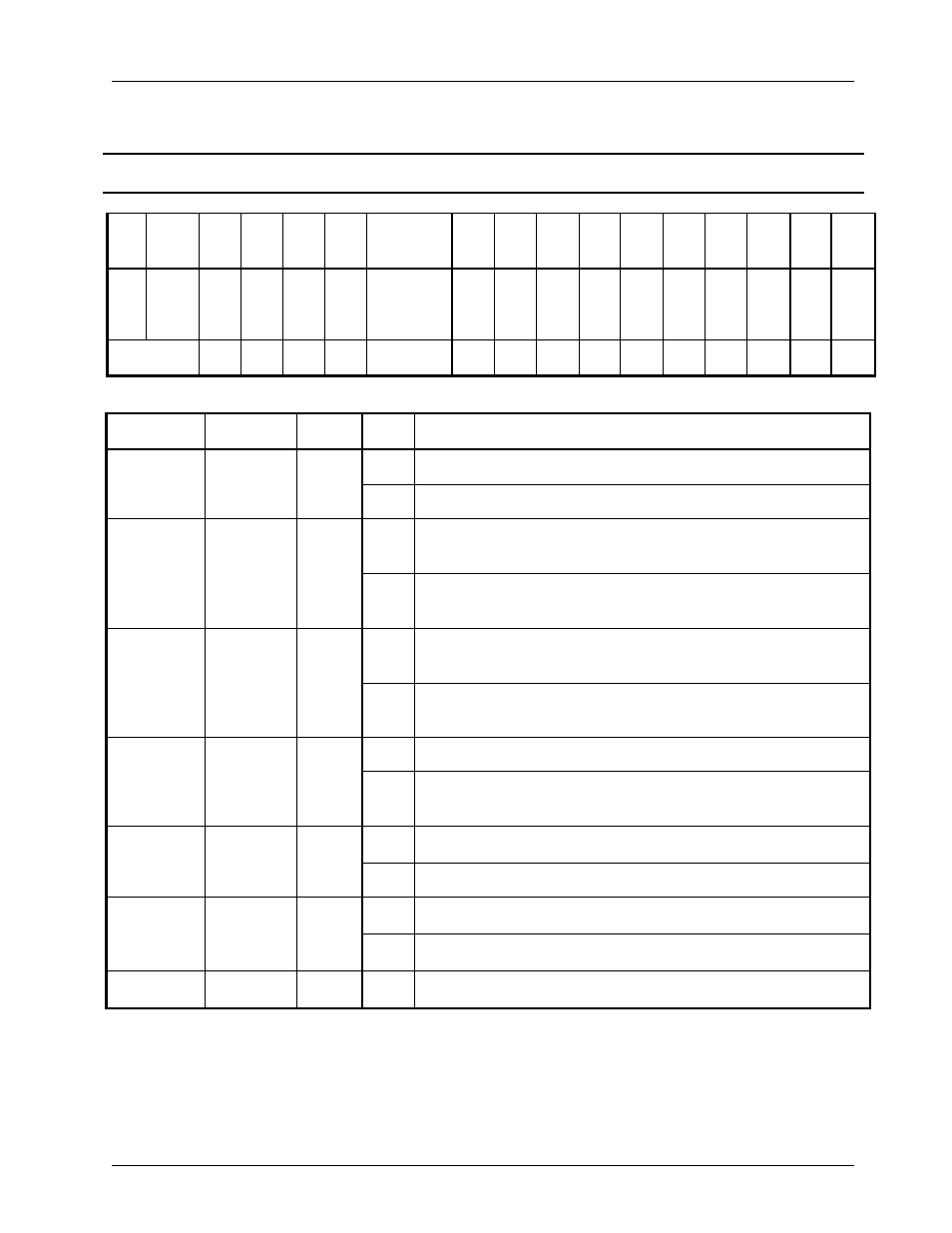

7.2. flag & status Register

flag & status register indicates the status of this LSI and data access inquiries.

AD

R/W

Bit

15

Bit

14

Bit

13

Bit

12

Bit

11

Bit

10

Bit

9

Bit

8

Bit

7

Bit

6

Bit

5

Bit

4

Bit

3

Bit

2

Bit

1

Bit

0

02h

R

IPC

busy

tran

ready

tran

busy

ISO

cycle

A-Tx-

buff

empty

A-Rx-

buff

empty

-

-

-

-

-

sleep

data

req

recv

busy

cmstr

INT

Initial Value

‘0’

‘0’

‘0’

‘0’

‘1’

‘1’

‘0’

‘0’

‘0’

‘0’

‘0’

‘0’

‘0’

‘0’

‘0’

‘0’

BIT

Bit Name

Action

Value

Function

0

Indicates that receipt of instruction is available.

15

IPC busy

Read

1

Indicates that receipt of instruction is not available.

0

Indicates that bus reset or forced sleep is being executed, and transmit/receive of

packet is unavailable.

14

tran ready

Read

1

Indicates that bus reset is completed and forced sleep is not being executed, and

transmit/receive of packet is available.

0

Indicates that packet transmit is not being executed or in the process of packet

receive addressed to this node.

13

tran busy

Read

1

Indicates that packet transmit is being executed or in the process of packet receive

addressed to this node.

0

Indicates that Isochronous cycle is not being executed.

12

ISO cycle

Read

1

Indicates that Isochronous cycle is being executed by transmit or receive of cycle

start packet.

0

Indicates that Asynchronous transmit specific buffer is not empty.

11

A-T x-buff

Empty

Read

1

Indicates that Asynchronous transmit specific buffer is empty.

0

Indicates that Asynchronous receive specific buffer is not empty.

10

A-Rx-buff

Empty

Read

1

Indicates that Asynchronous receive specific buffer is empty.

9 – 5

reserved

Read

0

Always indicate ‘0’.