FUJITSU MB86617A User Manual

Page 116

LSI S pecification

MB86617A

Rev.1.0

Fujitsu VLSI

111

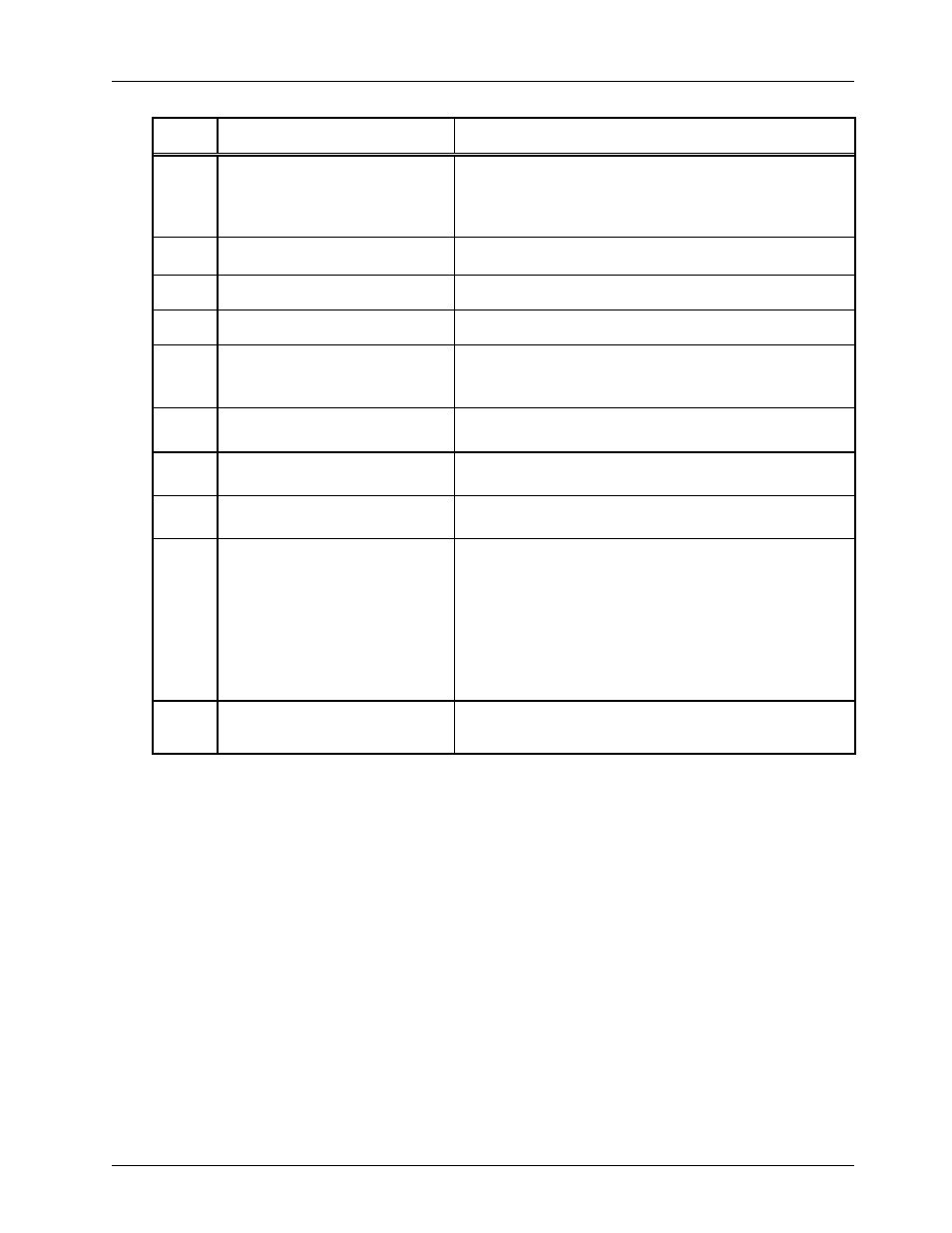

Interrupt

Interrupt Item

Description

INT23

Cycle start packet received

Received cycle start packet normally when self node is not root

> Isochronous cycle starts.

Set ISO cycle Bit (Bit12) of flag & status register (address 02h) at ‘1’

simaltaneously with this interrupt report.

INT24

Cycle start packet send

Completed to send Cycle start packet when self node is root.

INT25

Physical packet send

Completed to send Physical packet.

INT26

Extended PHY packet received

Received Extended PHY packet normally.

INT27

Physical configuration packet

received

Received Physical configuration packet normally.

> Reflect to Physical register#01(address Phy/Link-reg 02h) and switch

to specified performance automatically.

INT28

Link on packet received

Received Link-on packet addressed to self-node normally.

> Assert LINKON terminal output simultaneously.

INT29

Self-ID packet received

Received Self -ID packet normally.

Store data at ASYNC receive specific buffer.

INT30

Receive late occurred

Receive-late was occured.

Delete packet received.

INT31

Instruction abort (State)

Though Instruction was issued, it was not accepted bec ause the content

was not appropriate for this device.

e.g.) >Issued “ Remove sleep” (02h) instruction in spite of not in sleep

condition.

>Issued “Instruction suspend”(62h) instruction without instruction

to be stopped.

>Used undefine operand against issued instruction.

>Issued instruction was undefined.

etc.

INT32

Transmit late occurred

Transmit -late was occured.

>Delete packet transmitted.