FUJITSU DL3800 User Manual

Page 217

Interface

D-5

User's Manual

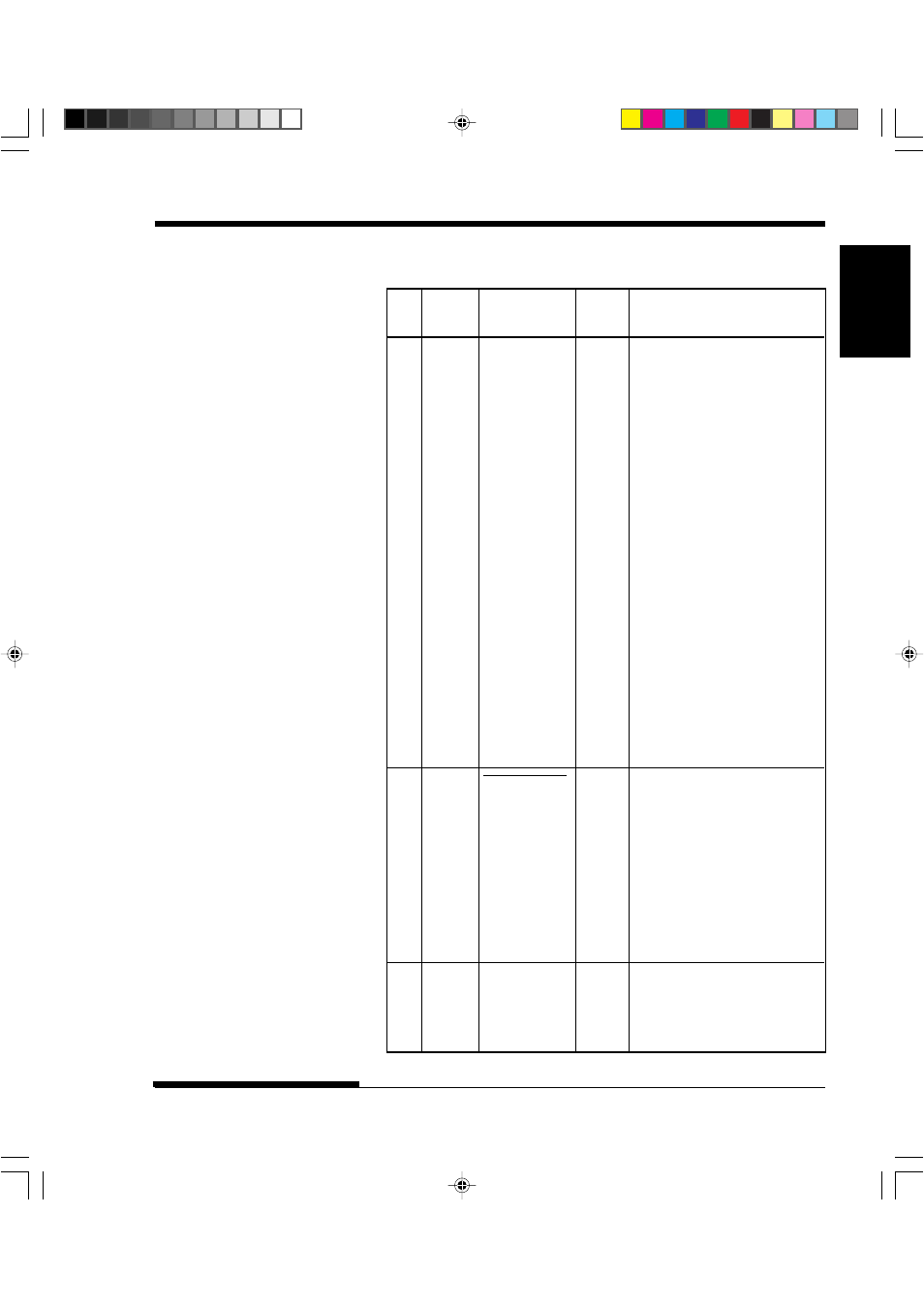

Pin

Return

Signal

Direc-

Description

No. Pin No.

name

tion

14

–

Host Busy

Input

Reverse data transfer phase:

This signal is set low when the

host can receive data, and

goes high when the host has

received data. Following a

reverse data transfer, the

interface enters the reverse

idle phase when the Host

Busy signal goes low and the

printer has no data.

Reverse idle phase:

This signal goes high when

the Printer Clock signal goes

low so that the interface re-

enters the reverse data

transfer phase. If it goes high

with the 1284 Active signal

low, the 1284 idle phase is

aborted and the interface

returns to the compatibility

mode.

32

–

Data Available Output Reverse data transfer phase:

This signal is set low when the

printer is ready to send data

to the host. During the data

transfer, it is used as data bit 0

(LSB), then data bit 4.

Reverse idle phase:

This signal is used to indicate

that data is available.

36

–

1284 Active

Input

This signal goes high to cause

the printer to enter the reverse

data transfer phase (nibble

mode).

INTERFACE INFORMATION

#D Appendix D

2000.09.20, 2:47 PM

5