FUJITSU DL3800 User Manual

Page 216

User's Manual

D-4

INTERFACE INFORMATION

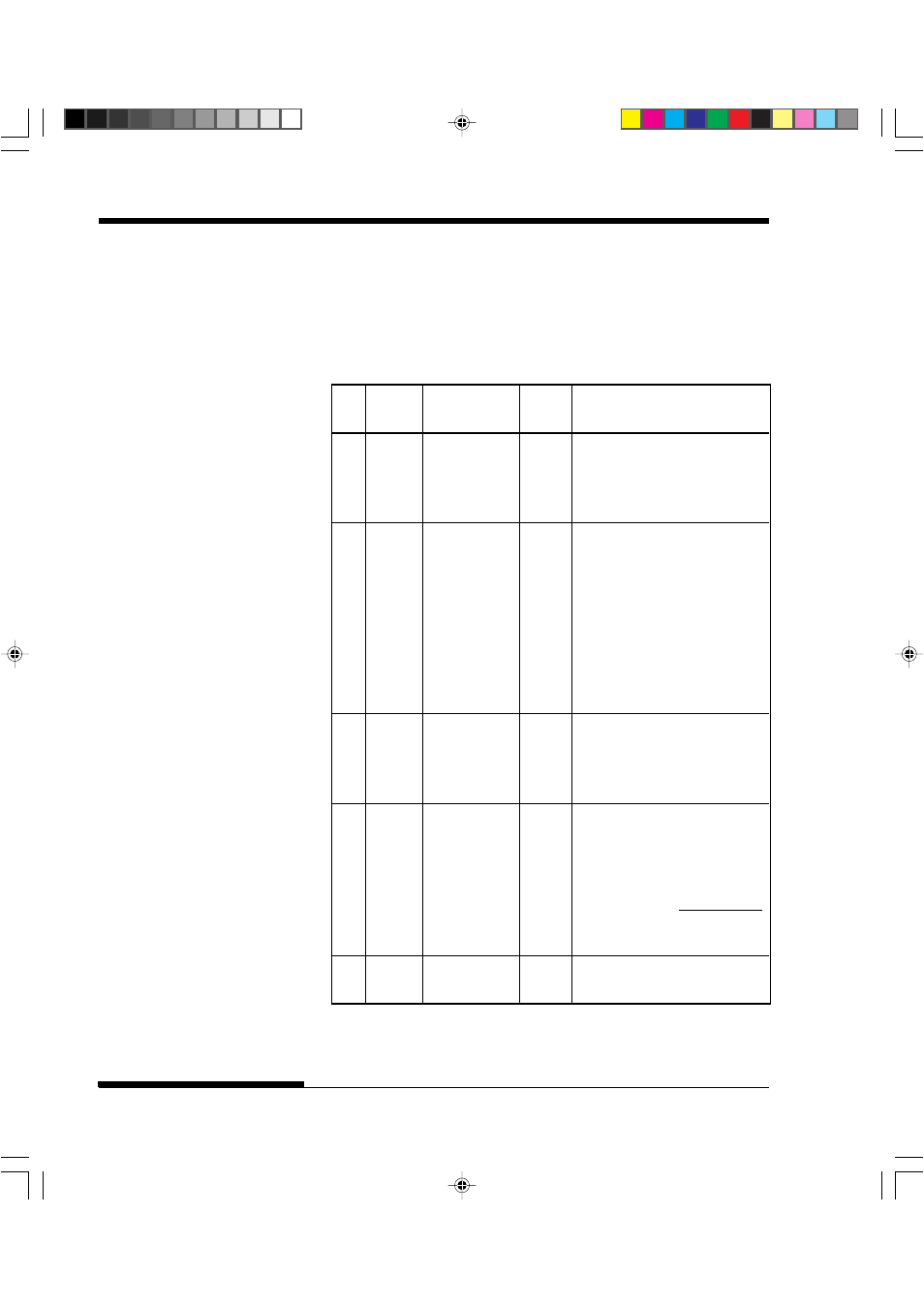

Nibble Mode

Pin numbers 2 to 9, 15 to 31, and 33 to 35 are the same as the conven-

tional mode.

Pin

Return

Signal

Direc-

Description

No. Pin No.

name

tion

1

19

Host Clock

Input

This signal is set high when

the host requests the reverse

data transfer phase (nibble

mode).

10

28

Printer Clock

Output Reverse data transfer phase:

This signal goes high when

data being sent to the host is

established.

Reverse idle phase:

This signal is set low then

goes high to interrupt the

host, indicating that data is

available.

11

29

Printer Busy

Output Reverse data transfer phase:

Data bit 3, data bit 7, then

forward path (host to printer)

busy status

12

30

Ack Data Req Output Reverse data transfer phase:

Data bit 2, then data bit 6

Reverse idle phase:

This signal is set high until the

host requests data and, after

that, follows the Data Available

signal.

13

–

X Flag

Output Reverse data transfer phase:

Data bit 1, then data bit 5

#D Appendix D

2000.09.20, 2:47 PM

4

- FTP-633GA1021 (6 pages)

- KA02038-Y820 (1 page)

- FTP-632MCL102 (7 pages)

- FTP-621MCL102 (6 pages)

- FTP-604 FTP-644MCL002 (7 pages)

- FTP-629MCL103-R (7 pages)

- FTP-641MCL351 (6 pages)

- C145-C037-01EN (123 pages)

- FTP-030P (3 pages)

- FTP-627USL401 (9 pages)

- FTP-621CT001 (6 pages)

- FTP-629MCL054 (7 pages)

- FTP-634MCL001 (7 pages)

- FTP-624MCL002 (8 pages)

- Printer (4 pages)

- FTP-040HF Holder Series (2 pages)

- P3PC-1442-01EN (17 pages)

- FTP-631MCL201 (6 pages)

- FTP-628WSL120 (7 pages)

- ScandAll PRO P2WW-2410-01ENZ0 (45 pages)

- DL6400Pro (247 pages)

- FTP-632MCL003 (7 pages)

- FTP-633MCL400 (12 pages)

- FTP-631MCL302 (6 pages)

- 102 (8 pages)

- FTP-622MCL302 (6 pages)

- FTP-642MCL302 (7 pages)

- 16DV (39 pages)

- FTP-639MCL103/383-R (7 pages)

- FTP-637MCL401 (6 pages)

- DL9400 (250 pages)

- M304X (143 pages)

- FTP-631MCL352 (6 pages)

- FTP-631MCL101 (6 pages)

- FTP-639MCL353 (7 pages)

- FTP-641MCL302 (6 pages)

- FTP-622DCL001/011 (8 pages)

- FTP-628MCL401 (9 pages)

- FTP-621MCL201 (6 pages)

- FTP-641MCL101/102 (6 pages)

- FTP-632MCL301 (6 pages)

- DL6400 (247 pages)

- FTP-627USL631 (10 pages)

- FTP-624MCL304 (7 pages)