Data acquisition – Dataman 520 Series User Manual

Page 21

DATAMAN oscilloscope

User’s Guide

MANUAL – One measuring cycle is executed immediately after activation from the

control panel.

2.2.3. Data acquisition

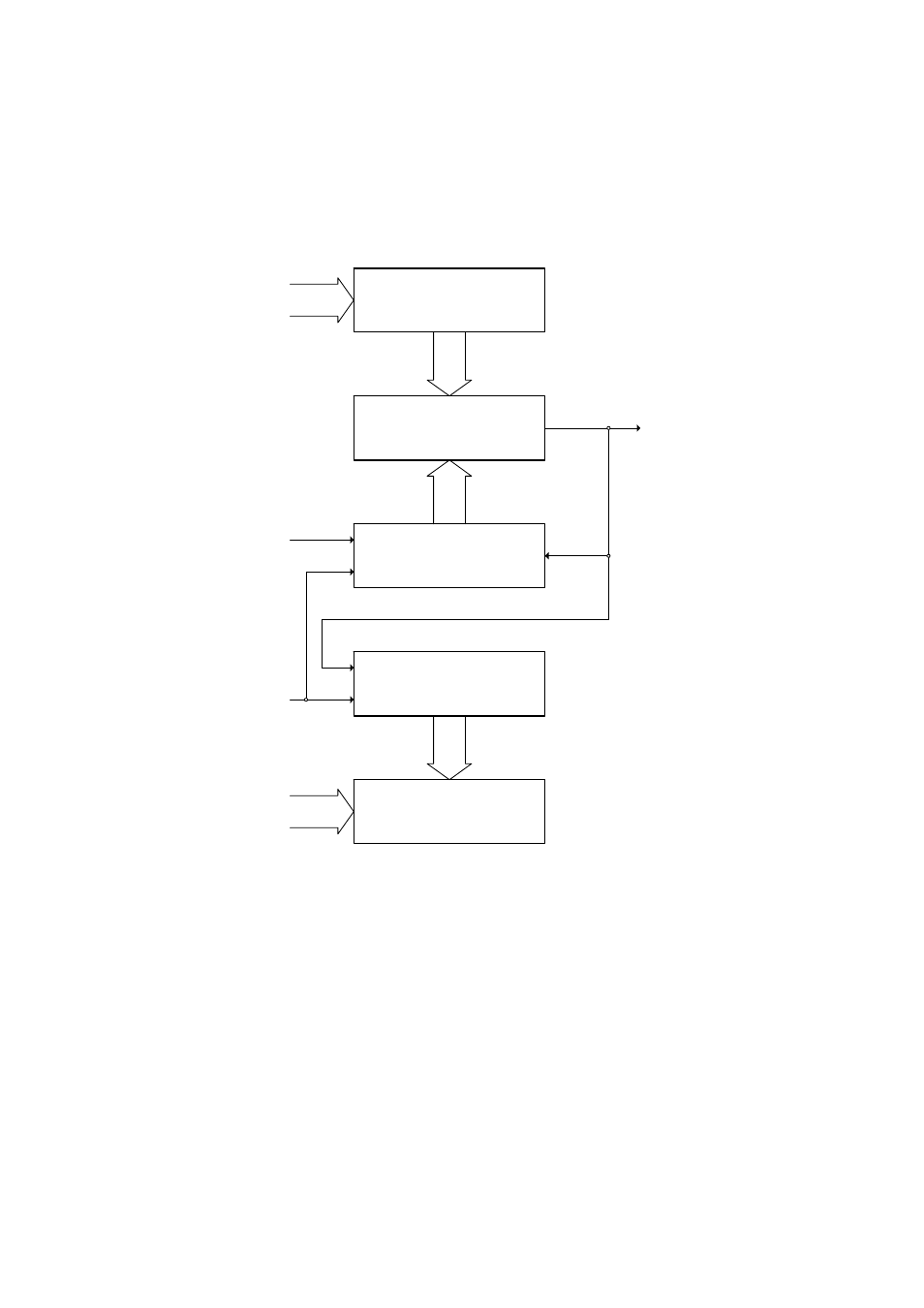

The simplified block schematics of data acquisition are shown in Figure 2.2.3.1.

REG

CMP

ACC

ADC

M

SD

DATA

A/B

clk

trg

done

Fig. 2.2.3.1. – Simplified block schematics of the data acquisition

The data from the AD converters is stored in the onboard memory M. This memory is

addressed by the address counter ADC, which starts to count immediately after the

start of measurement, regardless of trigger event. The occurrence of a valid trigger

event starts the after trigger data counter (ACC). The comparator CMP compares the

state of ACC with the output of register (REG), which contains the data amount

acquired after trigger. When the output of ACC reaches the value written to REG, the

comparator produces the signal (done), which stops both the ADC and ACC counters.

The amount of data written after the trigger to memory depends on the value of REG.

The value written to REG controls the relation of the trigger event and the displayed

data. By changing the value of REG it is possible to display data before, before and

after or only after the trigger. Because the length of the ACC counter is much longer

than the capacity of the onboard memory (more than 63000), it is possible to display

data delayed from the trigger event past the capacity of the onboard storage. However

the length of the displayed waveform is determined by the capacity of the onboard

- 21 -