Altera Stratix V Avalon-ST User Manual

Page 98

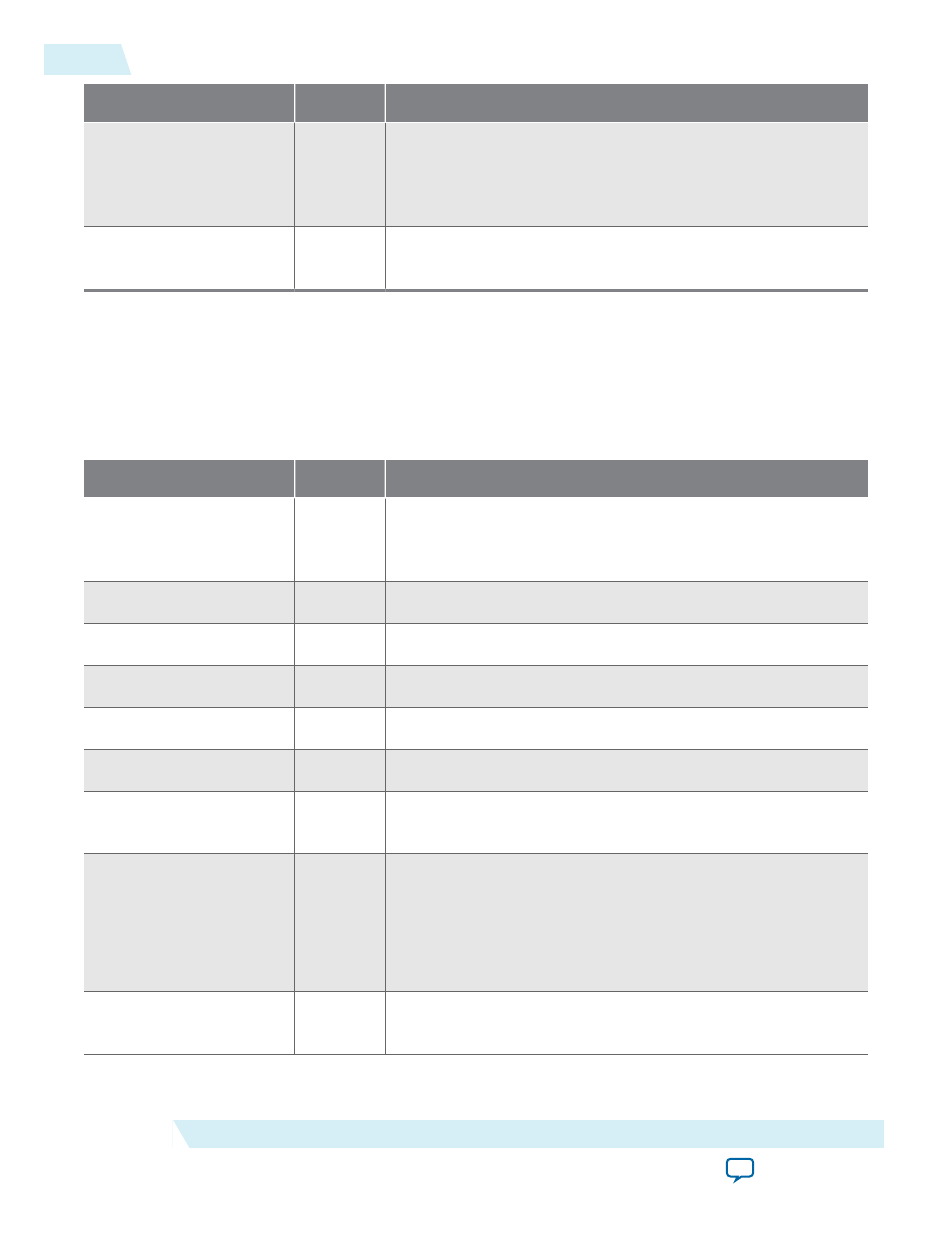

Signal Name

Direction

Description

link3_ctl[1]

Input

Link Control 3

Register

bit[1]:

Link Equalization Request

Interrupt Enable

. When set to 1, enables the generation of an

interrupt to indicate that the

Link Equalization Request

bit

has been set.

link3_ctl[0]

Input

Link Control 3

Register

bit [0].

Perform Equalization

.

When set to 1, the downstream port must perform equalization.

The following table describes the Configuration Space Bypass signals that are driven from the hard

Configuration Space in the Transaction Layer to the soft Configuration Space implemented in the

Application Layer. In Qsys, the Configuration Space Bypass output signals have the prefix

bypass_out_cfgbp_. In the MegaWizard Plug-In Manager design flow, these signals have the prefix cfgbp_.

All signals are synchronous to

pld_clk

.

Table 5-13: Configuration Space Bypass Mode Output Signals

Signal Name

Direction

Description

lane_err[7:0]

Output

When a bit is set to 1, indicates a lane error that is reported in the

Lane Error Status Register

of the Secondary PCI Express

Extended Capability structure. Bit 0 corresponds to lane 0.

link_equiz_req

Output

Reported as Bit 5 in the

Link Status 2 Register

.

equiz_complete

Output

Reported as Bit 1 in the

Link Status 2 Register

.

phase_3_successful

Output

Reported as Bit 4 in the

Link Status 2 Register

.

phase_2_successful

Output

Reported as Bit 3 in the

Link Status 2 Register

.

phase_1_successful

Output

Reported as Bit 2 in the

Link Status 2 Register

.

current_deemph

Output

Current de-emphasis setting reported in the

Lin

k Status 2

Register

.

current_speed[1:0]

Output

Current link speed as reported in the

Link Status Register

.

The following encodings are defined:

• 2'b01: Gen1

• 2'b10: Gen2

• 2'b11: Gen3

link_up

Output

When asserted indicates that the link is up and has exited the

Configuration.Idle state.

5-46

Configuration Space Bypass Mode Interface Signals

UG-01097_avst

2014.12.15

Altera Corporation

Interfaces and Signal Descriptions