Parity signals – Altera Stratix V Avalon-ST User Manual

Page 102

Parity Signals

You enable parity checking by selecting Enable byte parity ports on the Avalon-ST interface under the

System Settings heading of the parameter editor. Parity is odd. This option is not available for the

Avalon-MM Stratix V Hard IP for PCI Express. Parity protection provides some data protection in

systems that do not use ECRC checking.

On the RX datapath, parity is computed on the incoming TLP prior to the LCRC check in the Data Link

Layer. Up to 32 parity bits are propagated to the Application Layer along with the RX Avalon-ST data.

The RX datapath also propagates up to 32 parity bits to the Transaction Layer for Configuration TLPs. On

the TX datapath, parity generated in the Application Layer is checked in Transaction Layer and the Data

Link Layer.

The following table lists the signals that indicate parity errors. When an error is detected, parity error

signals are asserted for one cycle.

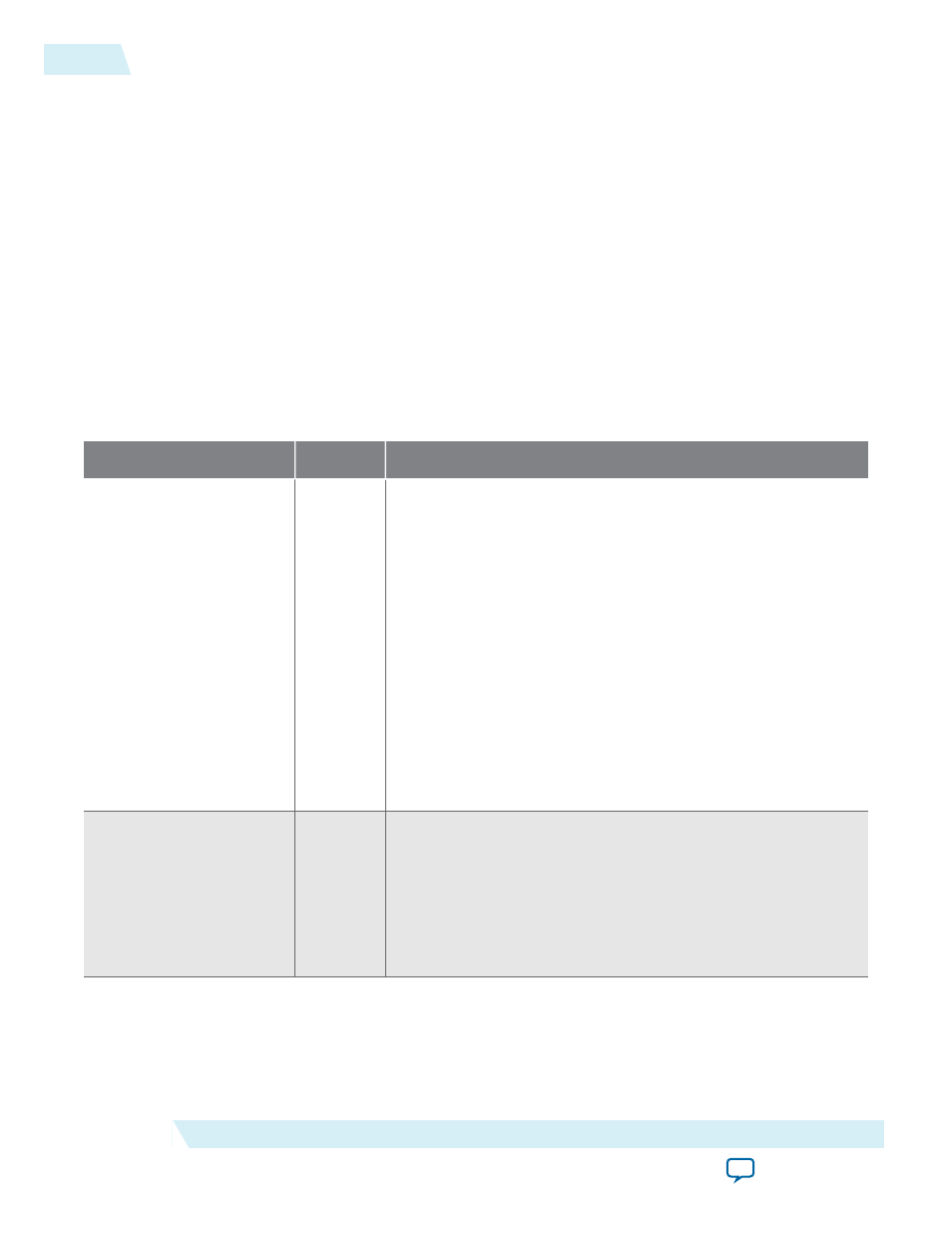

Table 5-14: Parity Signals

Signal Name

Direction

Description

tx_par_err[1:0]

Output

When asserted for a single cycle, indicates a parity error during

TX TLP transmission. These errors are logged in the VSEC

register. The following encodings are defined:

• 2’b10: A parity error was detected by the TX Transaction

Layer. The TLP is nullified and logged as an uncorrectable

internal error in the VSEC registers. For more information,

refer to Uncorrectable Internal Error Status Register.

• 2’b01: Some time later, the parity error is detected by the TX

Data Link Layer which drives 2’b01 to indicate the error.

Altera recommends resetting the Stratix V Hard IP for PCI

Express when this error is detected. Contact Altera if resetting

becomes unworkable.

Note that not all simulation models assert the Transaction Layer

error bit in conjunction with the Data Link Layer error bit.

rx_par_err

Output

When asserted for a single cycle, indicates that a parity error was

detected in a TLP at the input of the RX buffer. This error is

logged as an uncorrectable internal error in the VSEC registers.

For more information, refer to Uncorrectable Internal Error

Status Register. If this error occurs, you must reset the Hard IP if

this error occurs because parity errors can leave the Hard IP in an

unknown state.

5-50

Parity Signals

UG-01097_avst

2014.12.15

Altera Corporation

Interfaces and Signal Descriptions