Bar/address map – Altera Stratix V Avalon-ST User Manual

Page 220

• altpcierd_read_dma_requester, altpcierd_read_dma_requester_128—For each descriptor located in

the altpcierd_descriptor FIFO, this module transfers data from the BFM shared memory to the

Endpoint memory by issuing MRd PCI Express transaction layer packets.

altpcierd_read_dma_requester is used with the 64-bit Avalon-ST IP core.

altpcierd_read_dma_requester_128 is used with the 128-bit Avalon-ST IP core.

• altpcie rd_write_dma_requester, altpcierd_write_dma_requester_128—For each descriptor located

in the altpcierd_descriptor FIFO, this module transfers data from the Endpoint memory to the BFM

shared memory by issuing MWr PCI Express transaction layer packets. altpc

ierd_write_dma_requester is used with the 64-bit Avalon-ST IP core.

altpcierd_write_dma_requester_128 is used with the 128-bit Avalon-ST IP core.ls

• altpcierd_cpld_rx_buffer—This modules monitors the available space of the RX Buffer; It prevents

RX Buffer overflow by arbitrating memory read request issued by the application.

• altpcierd_cplerr_lmi—This module transfers the err_desc_func0 from the application to the Hard IP

block using the LMI interface. It also retimes the

cpl_er

r bits from the application to the Hard IP

block.

• altpcierd_tl_cfg_sample—This module demultiplexes the Configuration Space signals from the

tl_cfg_ctl

bus from the Hard IP block and synchronizes this information, along with the

tl_cfg_sts

bus to the user clock (

pld_clk

) domain.

Related Information

•

on page 5-76

•

Chaining DMA Control and Status Registers

on page 17-10

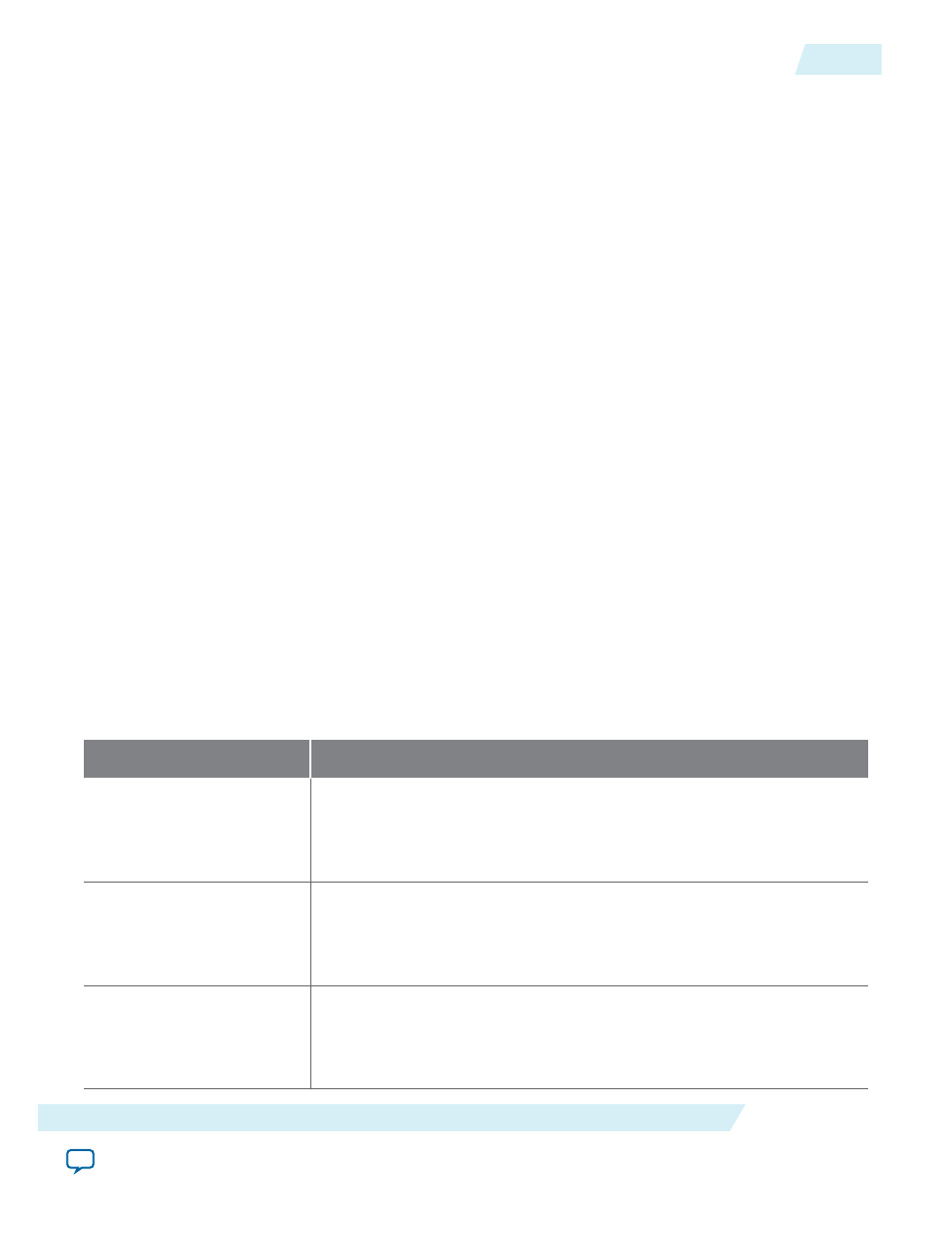

BAR/Address Map

The design example maps received memory transactions to either the target memory block or the control

register block based on which BAR the transaction matches. There are multiple BARs that map to each of

these blocks to maximize interoperability with different variation files. The following table shows the

mapping.

Table 17-1: BAR Map

Memory BAR

Mapping

32-bit BAR0

32-bit BAR1

64-bit BAR1:0

Maps to 32 KByte target memory block. Use the rc_slave module to bypass

the chaining DMA.

32-bit BAR2

32-bit BAR3

64-bit BAR3:2

Maps to DMA Read and DMA write control and status registers, a

minimum of 256 bytes.

32-bit BAR4

32-bit BAR5

64-bit BAR5:4

Maps to 32 KByte target memory block. Use the rc_slave module to bypass

the chaining DMA.

UG-01097_avst

2014.12.15

BAR/Address Map

17-9

Testbench and Design Example

Altera Corporation