Vendor specific extended capability (vsec), Phy characteristics – Altera Stratix V Avalon-ST User Manual

Page 52

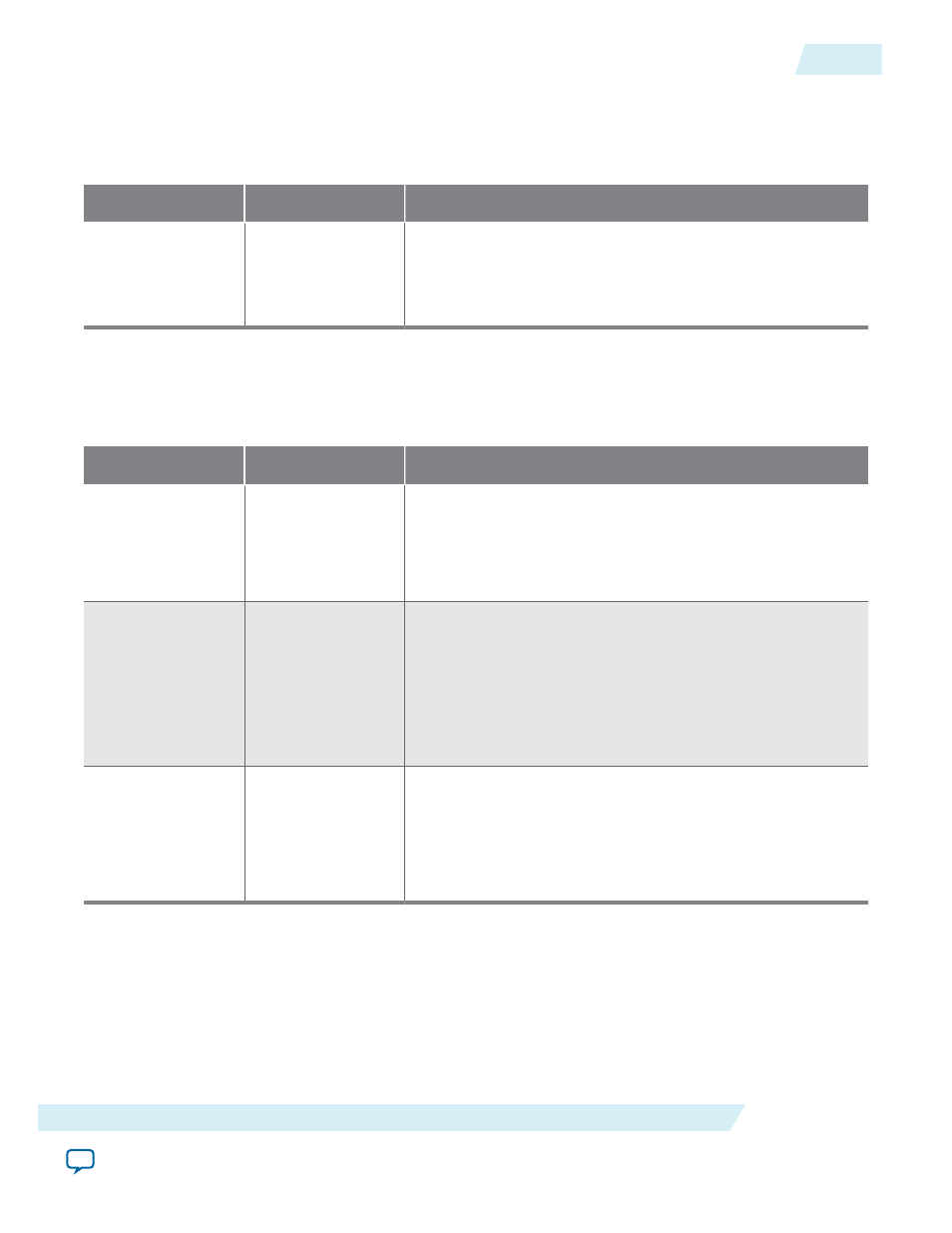

Vendor Specific Extended Capability (VSEC)

Table 4-11: VSEC

Parameter

Value

Description

User ID register

from the Vendor

Sepcific Extended

Capability

Custom value

Sets the read-only value of the 16-bit User ID register from the

Vendor Specific Extended Capability. This parameter is only

valid for Endpoints.

PHY Characteristics

Table 4-12: PHY Characteristics

Parameter

Value

Description

Gen2 transmit

deemphasis

3.5dB

6dB

Specifies the transmit de-emphasis for Gen2. Altera

recommends the following settings:

• 3.5dB: Short PCB traces

• 6.0dB: Long PCB traces.

Use ATX PLL

On/Off

When enabled, the Hard IP for PCI Express uses the ATX PLL

instead of the CMU PLL Using the ATX PLL instead of the

CMU PLL reduces the number of transceiver channels that are

necessary for Gen1 and Gen2 variants. This option requires

the use of the soft reset controller and does not support the

CvP flow. For more information about channel placement,

refer to

Enable Common

Clock Configura‐

tion (for lower

latency)

On/Off

When you turn this option on, the Application Layer and

Transaction Layer use a common clock. Using a common

clock reduces datapath latency because synchronizers are not

necessary.

This parameter is only available for the Avalon-ST interface.

UG-01097_avst

2014.08.18

Vendor Specific Extended Capability (VSEC)

4-15

Parameter Settings

Altera Corporation