Configurations – Altera Stratix V Avalon-ST User Manual

Page 8

Configurations

The Stratix V Hard IP for PCI Express includes a full hard IP implementation of the PCI Express stack

including the following layers:

• Physical (PHY), including:

• Physical Media Attachment (PMA)

• Physical Coding Sublayer (PCS)

• Media Access Control (MAC)

• Data Link Layer (DL)

• Transaction Layer (TL)

The Hard IP supports all memory, I/O, configuration, and message transactions. It is optimized for Altera

devices. The Application Layer interface is also optimized to achieve maximum effective throughput. You

can customize the Hard IP to meet your design requirements.

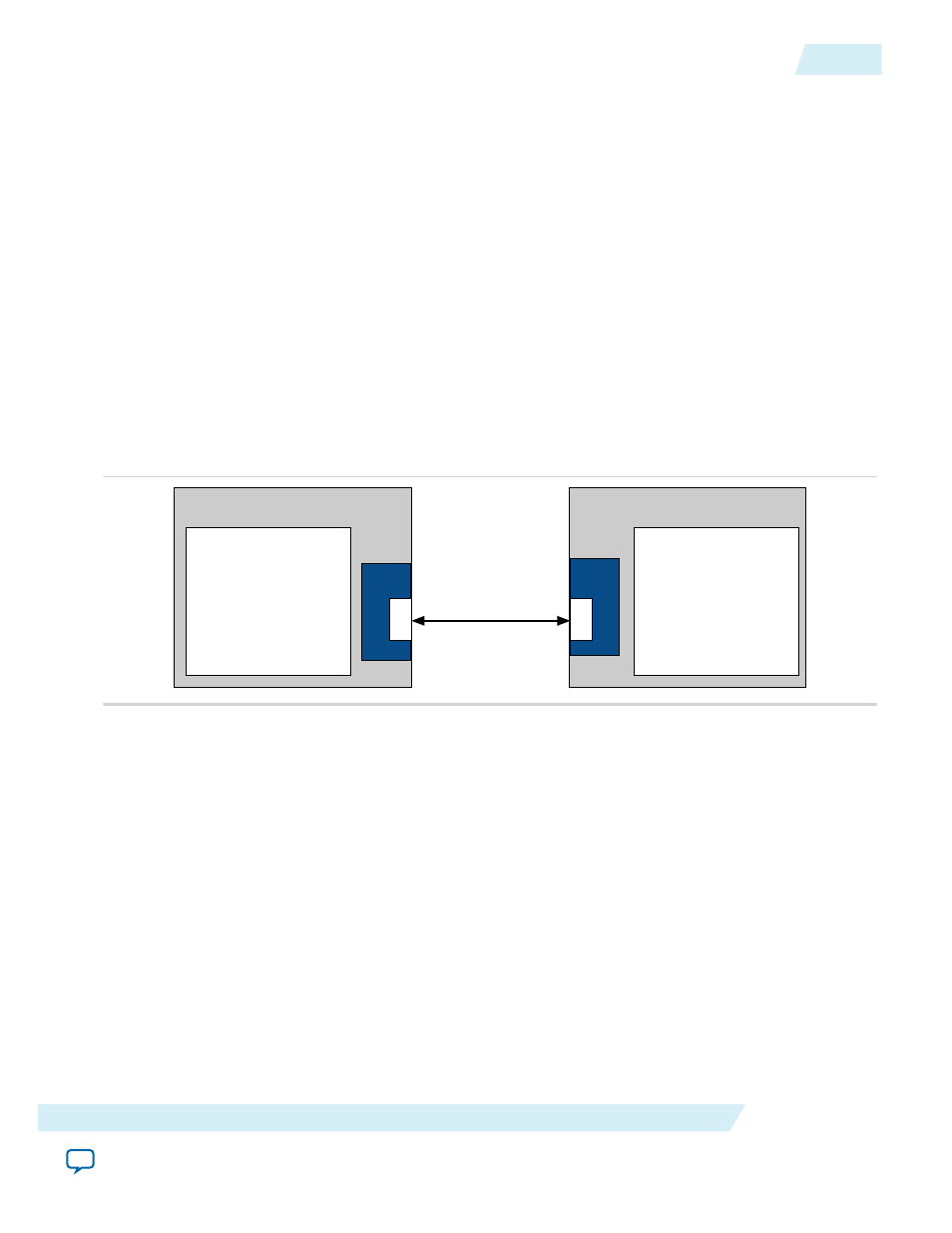

Figure 1-2: PCI Express Application with a Single Root Port and Endpoint

The following figure shows a PCI Express link between two Stratix V FPGAs.

Altera FPGA

User Application

Logic

PCIe

Hard IP

RP

PCIe

Hard IP

EP

User Application

Logic

PCI Express Link

Altera FPGA

Figure 1-3: PCI Express Application Using Configuration via Protocol

The Stratix V design below includes the following components:

• A Root Port that connects directly to a second FPGA that includes an Endpoint.

• Two Endpoints that connect to a PCIe switch.

• A host CPU that implements CvP using the PCI Express link connects through the switch. For more

information about configuration over a PCI Express link, refer to

Configuration via Protocol (CvP)

on page 14-1.

UG-01097_avst

2014.12.15

Configurations

1-7

Datasheet

Altera Corporation