Avalon-st example designs – Altera Stratix V Avalon-ST User Manual

Page 9

PCIe Link

PCIe Hard IP

RP

Switch

PCIe

Hard IP

RP

User Application

Logic

PCIe Hard IP

EP

PCIe Link

PCIe Link

User Application

Logic

Altera FPGA Hard IP for PCI Express

Altera FPGA with Hard IP for PCI Express

Active Serial or

Active Quad

Device Configuration

Configuration via Protocol (CvP)

using the PCI Express Link

Serial or

Quad Flash

USB

Download

cable

PCIe

Hard IP

EP

User

Application

Logic

Altera FPGA with Hard IP for PCI Express

Config

Control

CVP

USB

Host CPU

PCIe

Related Information

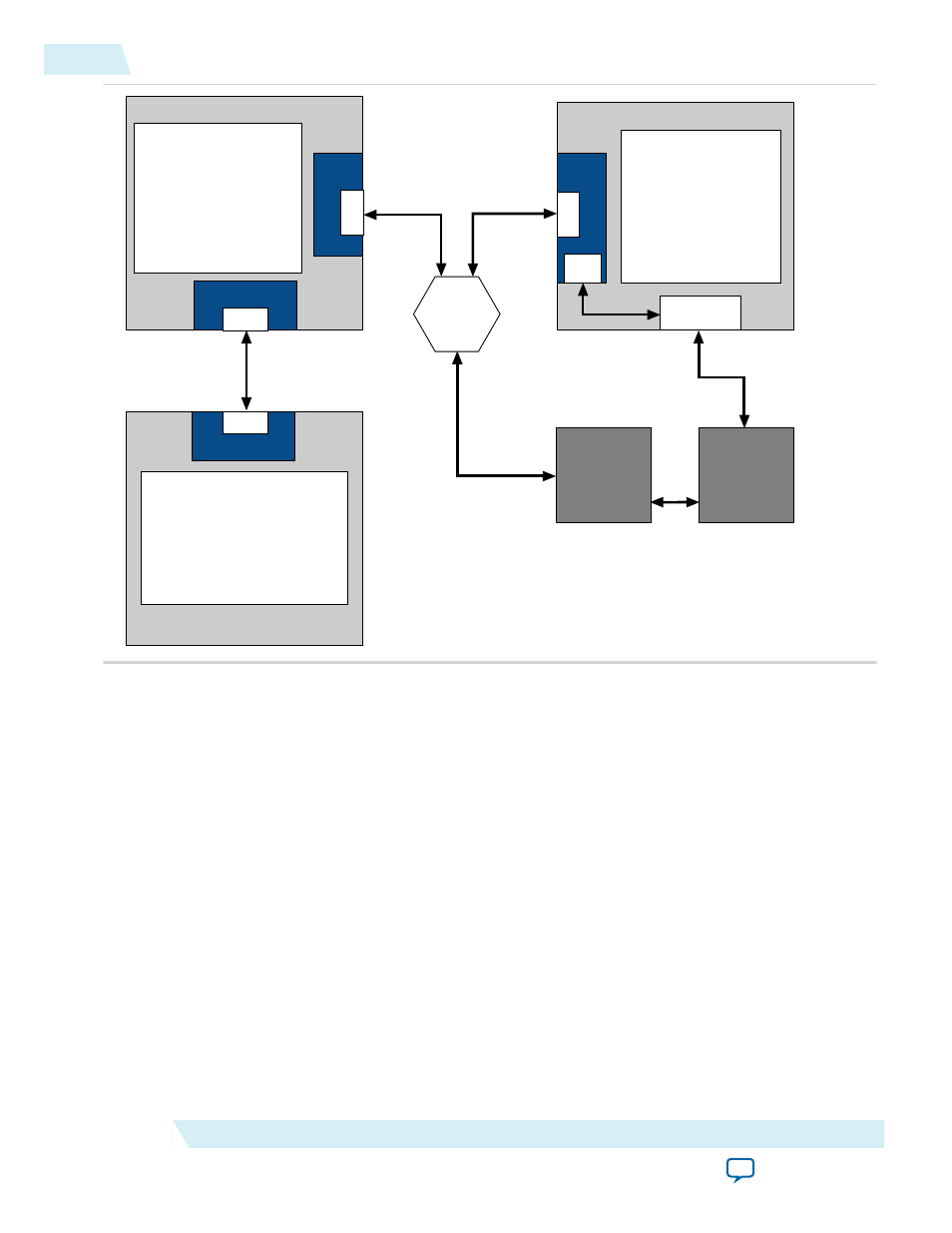

Avalon-ST Example Designs

Altera provides example designs to familiarize you with the available functionality. Each design connects

the device under test (DUT) to an application programming platform (APP), labeled APPs in the figure

below. Certain critical parameters of the APPs component are set to match the values of the DUT. If you

change these parameters, you must change the APPs component to match. You can change the values for

all other parameters of the DUT without editing the APPs component.

1-8

Avalon-ST Example Designs

UG-01097_avst

2014.12.15

Altera Corporation

Datasheet