Configuration space bypass mode interface signals – Altera Stratix V Avalon-ST User Manual

Page 96

Configuration Space Bypass Mode Interface Signals

In Configuration Space Bypass mode, the soft Configuration Space exchanges control and status informa‐

tion with the Stratix V Hard IP for PCI Express’s Transaction, Data Link and PHY Layers. Refer to

Configuration Space Bypass Modefor information about the division of the Configuration Space function‐

ality in bypass mode.

The following table describes the input signals which are driven from the Application Layer’s soft

Configuration Space to the Transaction Layer’s hard Configuration Space. All signals are synchronous to

pld_clk

.

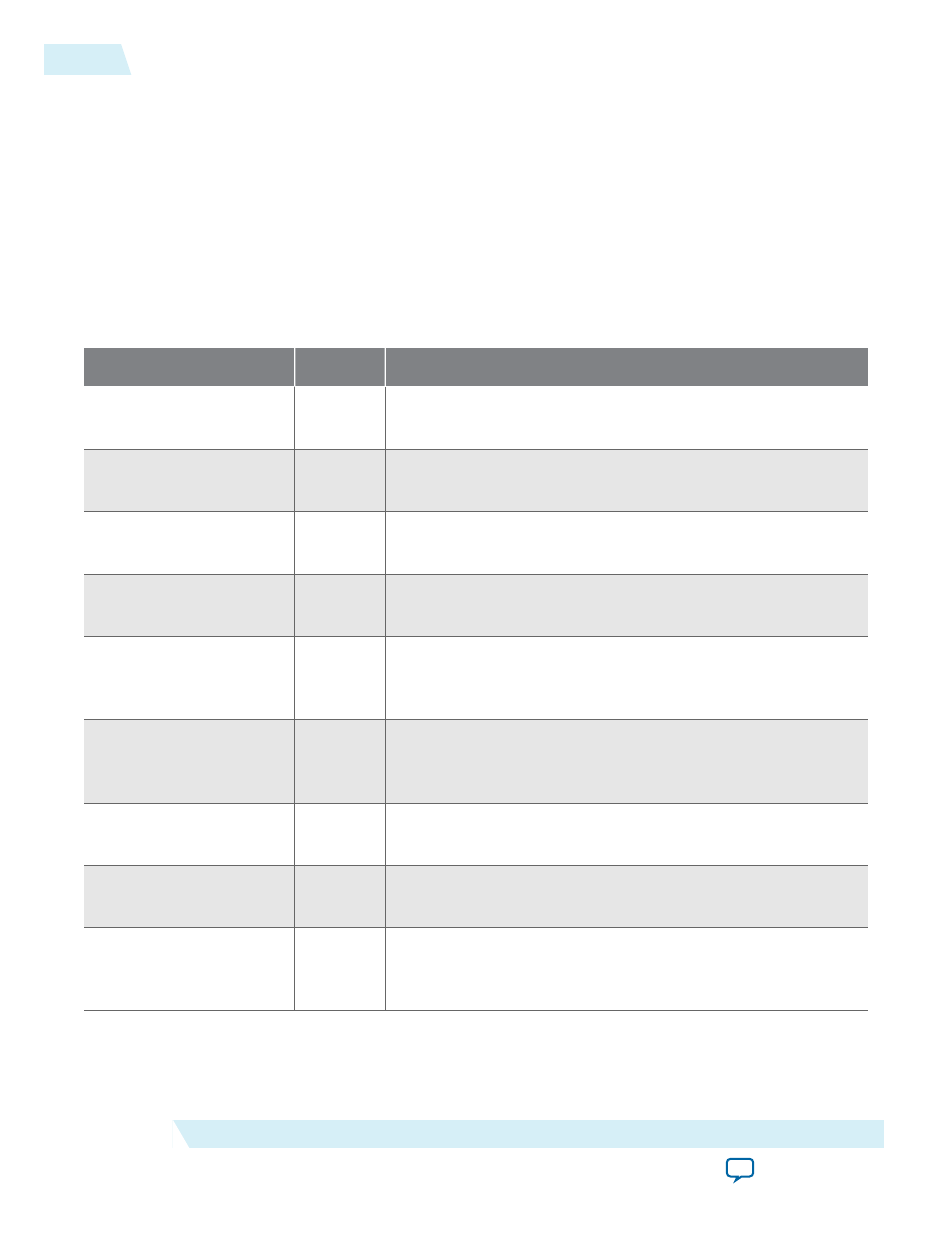

Table 5-12: Configuration Space Bypass Mode Input Signals

Signal Name

Direction

Description

link2csr[12:0]

Input

Bits[12:0] of the

link2csr

register from the soft Configuration

Space.

comclk_reg

Input

Common clock configuration bit of the

Link Control

Register

in the soft Configuration Space.

extsy_reg

Input

Extended synchronization bit of the

Link Control

Register

in

the soft Configuration Space.

max_pload[2:0]

Input

MAX_PAYLOAD_SIZE

field of the

Device Control

Register

in the

soft Configuration Space.

tx_ecrcgen

Input

ECRC Generation Enable

which is bit 6 of the

Advanced Error

Capabilities and Control

Register

(0x18) in the soft

Configuration Space.

rx_ecrchk

Input

ECRC Check Enable

which is Bit 8 of the

Advanced Error

Capab

ilities and Control

Register

(0x18) in the soft

Configuration Space.

secbus[7]

Input

MSB of the

Secondary Bus Number

Register

in the soft

Configuration Space.

secbus[6:0]

Input

Low-order 7 bits of

Secondary Bus Number

Register

in the soft

Configuration Space.

linkcsr_bit0

Input

Active State Power Management

(ASPM)

Control

which is Bit

0 of the

Link Control

Register

in the soft Configuration Space.

ASPM is not supported.

5-44

Configuration Space Bypass Mode Interface Signals

UG-01097_avst

2014.12.15

Altera Corporation

Interfaces and Signal Descriptions