Maxim Integrated MAXQ622 User Manual

Page 84

MAXQ612/MAXQ622 User’s Guide

Maxim Integrated

5-11

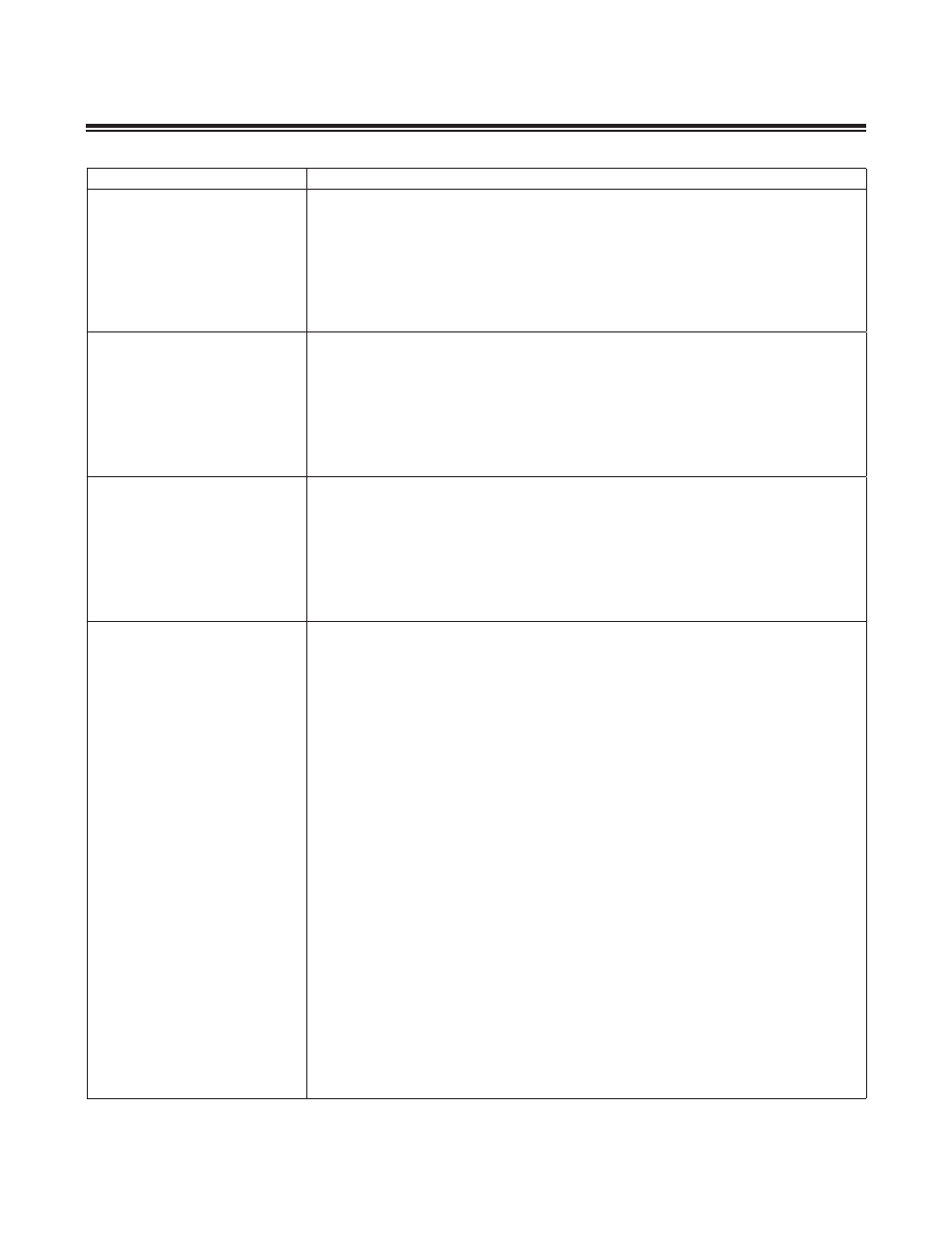

REGISTER

DESCRIPTION

PI4 (08h, 01h)

Port 4 Input Register

Initialization:

The reset value for this register is dependent on the logical states of the pins .

Read/Write Access:

Unrestricted read .

PI4.7 to PI4.0

Port 4 Input Register Bits 7:0. The PI4 register always reflects the logic state of its pins

when read . Note that each port pin has a weak pullup circuit when functioning as an input

and the p-channel pullup transistor is controlled by its respective PO bits . If the PO bit is set

to 1, the weak pullup is on, if the PO bit is cleared to 0, the weak pullup is off and forces the

port pin into three-state .

PI5 (09h, 01h)

Port 5 Input Register

Initialization:

The reset value for this register is dependent on the logical states of the pins .

Read/Write Access:

Unrestricted read .

PI5.7 to PI5.0

Port 5 Input Register Bits 7:0. The PI5 register always reflects the logic state of its pins

when read . Note that each port pin has a weak pullup circuit when functioning as an input

and the p-channel pullup transistor is controlled by its respective PO bits . If the PO bit is set

to 1, the weak pullup is on, if the PO bit is cleared to 0, the weak pullup is off and forces the

port pin into three-state .

PI6 (0Ah, 01h)

Port 6 Input Register

Initialization:

The reset value for this register is dependent on the logical states of the pins .

Read/Write Access:

Unrestricted read .

PI6.7 to PI6.0

Port 6 Input Register Bits 7:0. The PI6 register always reflects the logic state of its pins

when read . Note that each port pin has a weak pullup circuit when functioning as an input

and the p-channel pullup transistor is controlled by its respective PO bits . If the PO bit is set

to 1, the weak pullup is on, if the PO bit is cleared to 0, the weak pullup is off and forces the

port pin into three-state .

PWCN (0Ch, 01h)

Power Control Register (16-bit register)

Initialization:

This register is set to 000000sss1100000b on all forms of reset .

Read/Write Access:

Unrestricted read/write .

PWCN.0 (PFD)

Power-Fail Monitor Disable. This bit determines whether the power-fail monitoring is

enabled in stop mode when the regulator is off (REGEN = 0) . When the regulator is enabled

(as in normal operation or when REGEN = 1 in stop mode), the power-fail monitoring is

always enabled, independent of the PFD bit setting . Otherwise, when set to 1, the power-

fail reset detection for DVDD is disabled when the device is placed into stop mode . When

placed into stop mode with PFD = 1 and REGEN = 0, the power-fail reset comparator shuts

down . When configured to 0 with REGEN = 0, the power-fail monitoring function is enabled

for detecting the condition DVDD < V

RST

during stop mode .

PWCN.1 (PFIE)

Power-Fail Monitor Interrupt Enable. Setting this bit to 1 generates an interrupt to the CPU

when PFI is set to 1 . Clearing this bit to 0 disables the interrupt from generating . The power-

fail monitor interrupt is not masked by the global interrupt enable (IGE) and is controlled

solely by the PFIE bit .

PWCN.2 (PFI)

Power-Fail Monitor Interrupt. This bit is set to 1 when the supply voltage falls below the

power-fail warning threshold . Clearing this bit to 0 clears the interrupt flag . However, if the

supply voltage is still below the threshold, this flag is set again . Setting this bit to 1 causes

an interrupt to the CPU when PFIE = 1 . The power-fail monitor interrupt is not masked by

the global interrupt enable (IGE) and is controlled solely by the PFIE bit .

It is not recommended to write to flash when the supply voltage drops below the power-fail

warning level as there is uncertainty in the duration of continuous power supply . The user

application should check the status of the PFI flag before initiating a flash program/erase

operation .

PWCN.3 (REGEN)

Regulator Enable. When set to 1, the internal regulator remains powered on when the

device is placed in stop mode . When cleared to 0, the internal regulator is shut down to

conserve power . The regulator is always enabled outside of stop mode, independent of the

REGEN bit setting .