6 memory protection, 2 .6 memory protection -16 – Maxim Integrated MAXQ622 User Manual

Page 20

MAXQ612/MAXQ622 User’s Guide

2-16

Maxim Integrated

2.6 Memory Protection

The MAXQ612/MAXQ622 support privilege levels for code . When enabled, code memory is separated into three areas .

Each area has an associated privilege level . RAM/utility ROM are assigned privilege levels as well:

• Code in the system area can be confidential. Code in the user areas can be prevented from reading and writing

system code .

• The user loader can be protected from user application code.

The PRIV register reflects the current execution privilege . Hardware guarantees that the contents of PRIV are never

higher than the maximum privilege level of the memory area the code is running from . For example, if user code were

trying to set PRIV to high, this would be prevented by hardware . However, any code can decide to lower the privilege

level at any time (see Equation 1) .

PRIV = min(maxprivilege(IP), PRIV) (Equation 1)

The bit contents of the PRIV register are shown in Table 2-5 . The convenient constants high/medium/low are defined

in Table 2-6, but all values from 00b to 11b can be used .

In addition to the PRIV register, the privilege level can also be set by writing to PRIVT0 and PRIVT1 in sequence . Again,

hardware guarantees that the contents of PRIVT0 are never higher than the maximum privilege level of the memory

area the code is running from .

When writing to PRIVT1, hardware modifies the PRIV register based on Equation 2 .

PRIV = min(PRIVT0, argument, maxprivilege(IP)) (Equation 2)

This means that, when using PRIVT[1:0], the privilege level cannot be raised unless all code between the writes to

PRIVT0 and PRIVT1 executes . Writing to PRIV automatically resets PRIVT0 to low .

In addition to the PRIV register, the privilege level can also be set by writing to PRIVT0 and PRIVT1 in sequence . Again,

hardware guarantees that the contents of PRIVT0 are never higher than the maximum privilege level of the memory

area the code is running from .

When writing to PRIVT1, hardware modifies the PRIV register based on

PRIV’ = min(PRIVT0, argument, maxprivilege(IP))

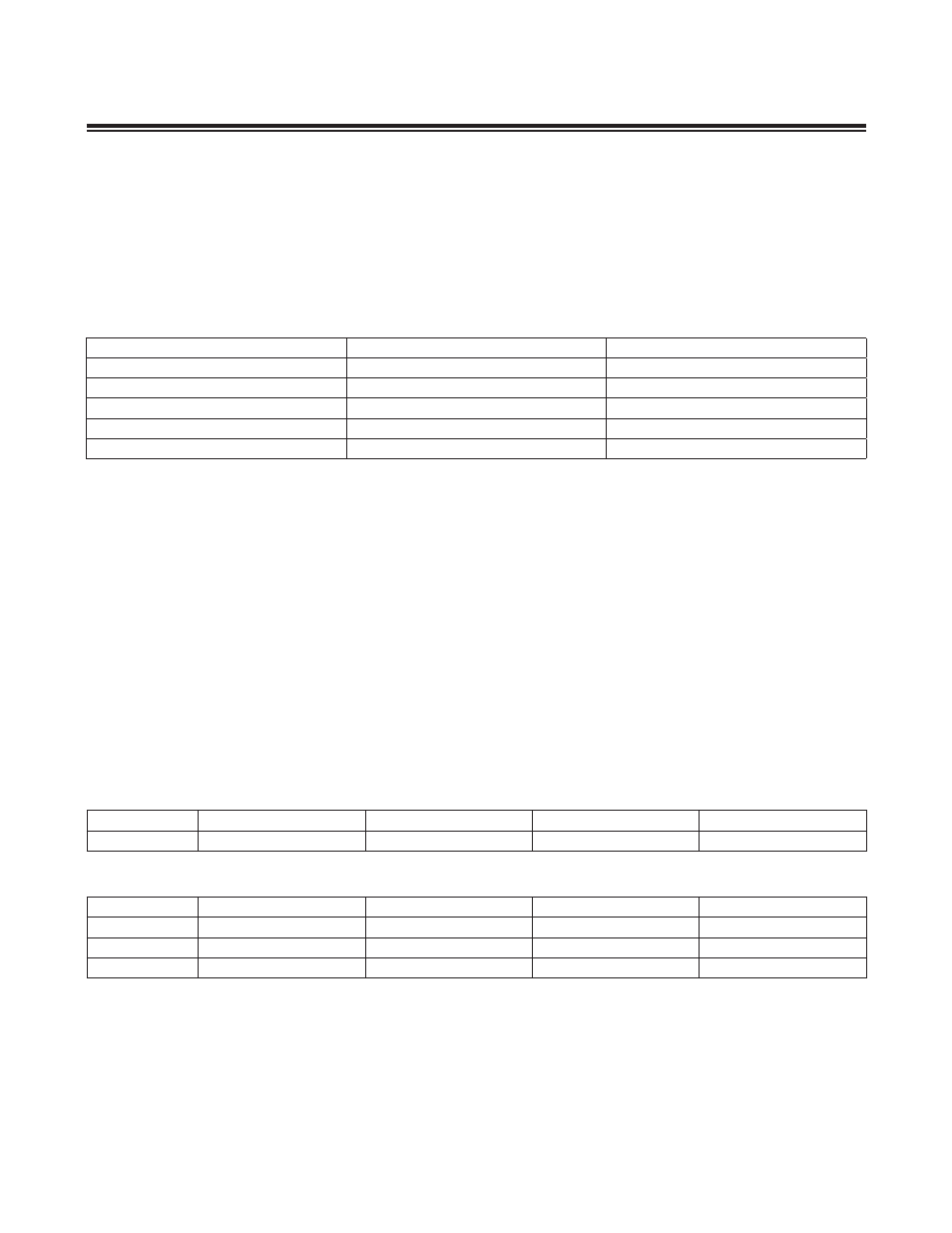

Table 2-4. Memory Areas and Associated Maximum Privilege Levels

Table 2-5. PRIV Register Bit Definitions

Table 2-6. Privilege Level Constants

AREA

PAGE ADDRESS

MAXIMUM PRIVILEGE LEVEL

System

0 to ULDR-1

High

User Loader

ULDR to UAPP-1

Medium

User Application

UAPP to top

Low

Utility ROM

N/A

High

Other (RAM)

N/A

Low

BIT

3

2

1

0

MEANING

System Write

System Read

User Loader Write

User Loader Read

BIT

3

2

1

0

HIGH

1

1

1

1

MEDIUM

0

0

1

1

LOW

0

0

0

0