10 using the watchdog timer, 3 .10 using the watchdog timer -18, Table 3-2. watchdog timer register control bits – Maxim Integrated MAXQ622 User Manual

Page 54

MAXQ612/MAXQ622 User’s Guide

3-18

Maxim Integrated

move @--DP[1], @DP[1]--

move @BP[--Offs], @BP[Offs--]

move @++DP[0], @DP[0]--

move @++DP[1], @DP[1]--

move @BP[++Offs], @BP[Offs--]

move @--DP[0], @DP[0]++

move @--DP[1], @DP[1]++

move @BP[--Offs], @BP[Offs++]

move @DP[0], @DP[0]++

move @DP[1], @DP[1]++

move @BP[Offs], @BP[Offs++]

move @DP[0], @DP[0]--

move @DP[1], @DP[1]--

move @BP[Offs], @BP[Offs--]

move DP[0], @DP[0]++

move DP[0], @DP[0]--

move DP[1], @DP[1]++

move DP[1], @DP[1]--

move Offs, @BP[Offs--]

move Offs, @BP[Offs++]

3.10 Using the Watchdog Timer

The watchdog timer is a user-programmable clock counter that can serve as a time-base generator, an event timer,

or a system supervisor . As shown in Figure 3-1, the main system clock drives the timer, which is supplied to a series

of dividers . If the watchdog interrupt and the watchdog reset are disabled (EWDI = 0 and EWT = 0), the watchdog

timer and its input clock are disabled . Whenever the watchdog timer is disabled, the watchdog interval timer (through

the WD[1:0] bits) and the 512-clock reset counter are reset if either the interrupt or reset function is enabled . When

the watchdog timer is initially enabled, there is a one- to three-clock-cycle delay before it starts . The divider output is

selectable and determines the interval between timeouts . When the timeout is reached, an interrupt flag is set, and,

if enabled, an interrupt occurs . A watchdog-reset function is also provided in addition to the watchdog interrupt . The

reset and interrupt are completely discrete functions that can be acknowledged or ignored, together or separately, for

various applications .

The watchdog timer reset function works as follows: After initializing the correct timeout interval (discussed below),

software can enable, if desired, the reset function by setting the enable watchdog timer reset (EWT = WDCN .1) bit .

Setting the EWT bit resets/restarts the watchdog timer if the watchdog interrupt is not already enabled . At any time

prior to reaching its user-selected terminal value, software can set the reset watchdog timer (RWT = WDCN .0) bit . If

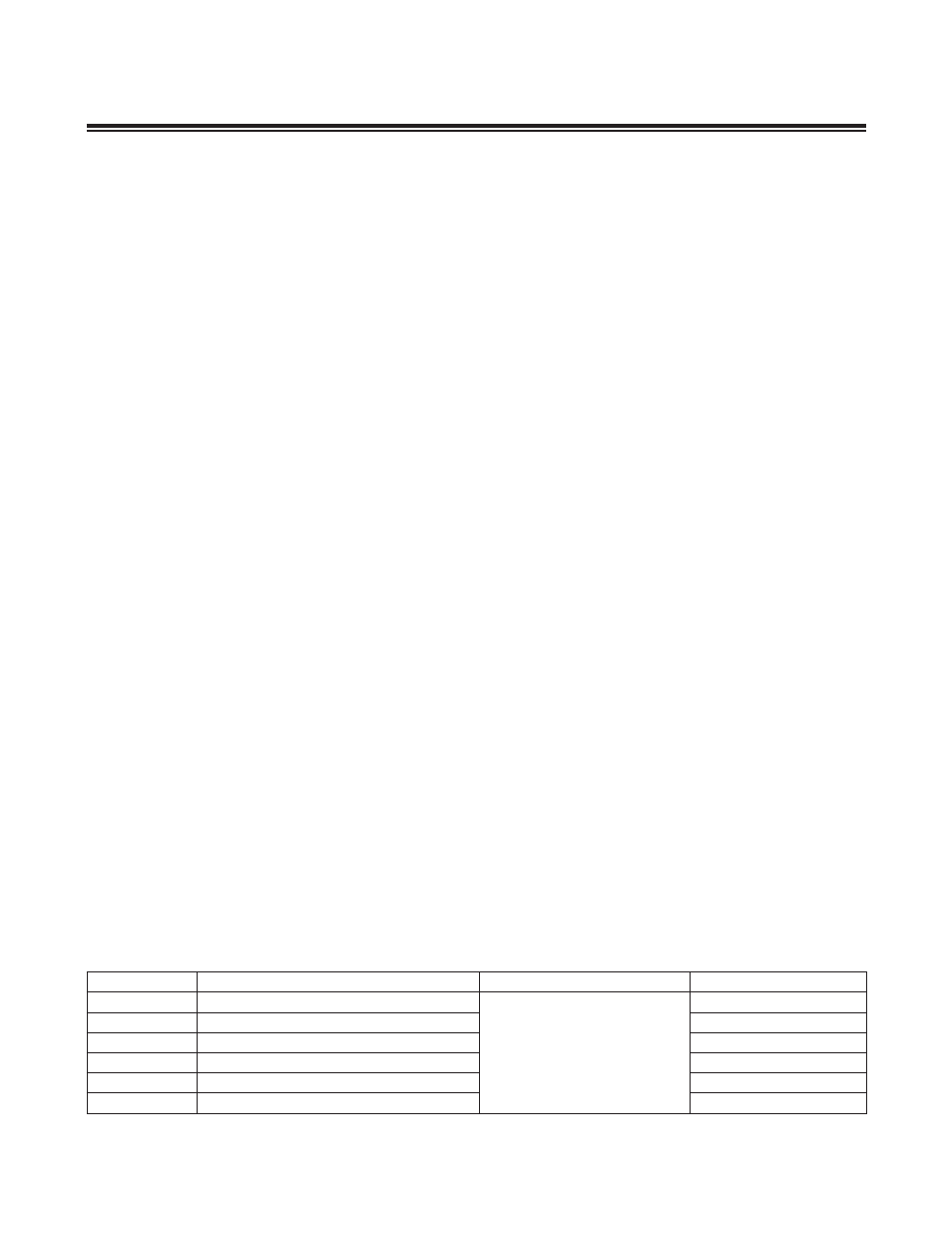

Table 3-2. Watchdog Timer Register Control Bits

BIT NAME

DESCRIPTION

REGISTER LOCATION

BIT POSITION

EWDI

Enable Watchdog Timer Interrupt

WDCN (0Fh, 8h)

WDCN .6

WD[1:0]

Watchdog Interval Control Bits

WDCN[5:4]

WDIF

Watchdog Interrupt Flag

WDCN .3

WTRF

Watchdog Timer Reset Flag

WDCN .2

EWT

Enable Watchdog Timer Reset

WDCN .1

RWT

Reset Watchdog Timer

WDCN .0