11 endpoint 0 byte count register (ep0bc), 12 endpoint 1 out byte count register (ep1bc), 13 endpoint 2 in byte count register (ep2bc) – Maxim Integrated MAXQ622 User Manual

Page 182

MAXQ612/MAXQ622 User’s Guide

12-12

Maxim Integrated

12.4.11 Endpoint 0 Byte Count Register (EP0BC)

Bit 7: Reserved. Reads returns zero.

Bits 6 to 0: EP0 Byte Count (EP0BC[6:0]). Endpoint 0 is a bidirectional endpoint, whereby both IN and OUT transfers

share the same buffer (endpoint 0 buffer) . The action of writing this register depends on the transfer direction . For an

IN transfer, the CPU writes the byte count to this register after loading the EP0 buffer with data . Valid values are 0 to

64 . When the CPU writes this register, the SIE arms the endpoint so that it returns a data packet instead of a NAK to

the next IN request to the endpoint . For an OUT transfer, the SIE loads the byte count to indicate the number of bytes

received in an OUT data transfer . When the OUT transfer is successful, the SIE ACKs the transfer, updates the byte

count register, and asserts the OUT0DAV interrupt bit . If the OUT0DAVIE is also enabled, this generates an interrupt

to the CPU .

12.4.12 Endpoint 1 OUT Byte Count Register (EP1BC)

Bit 7: Reserved. Reads returns zero.

Bits 6 to 0: EP1-OUT Byte Count (EP1BC[6:0]). This register contains the number of bytes the SIE received for a

successful EP1-OUT transfer and set the OUT1DAV bit to 1 . If the OUT1DAVIE is also enabled, this generates an inter-

rupt to the CPU .

12.4.13 Endpoint 2 IN Byte Count Register (EP2BC)

Bit 7: Reserved. Reads returns zero.

Bits 6 to 0: EP2-IN Byte Count (EP2BC[6:0]). This register contains the number of bytes the CPU has loaded into EP2

buffer for the next IN transfer . Writing to the EP2BC register arms endpoint 2 for the next IN transfer .

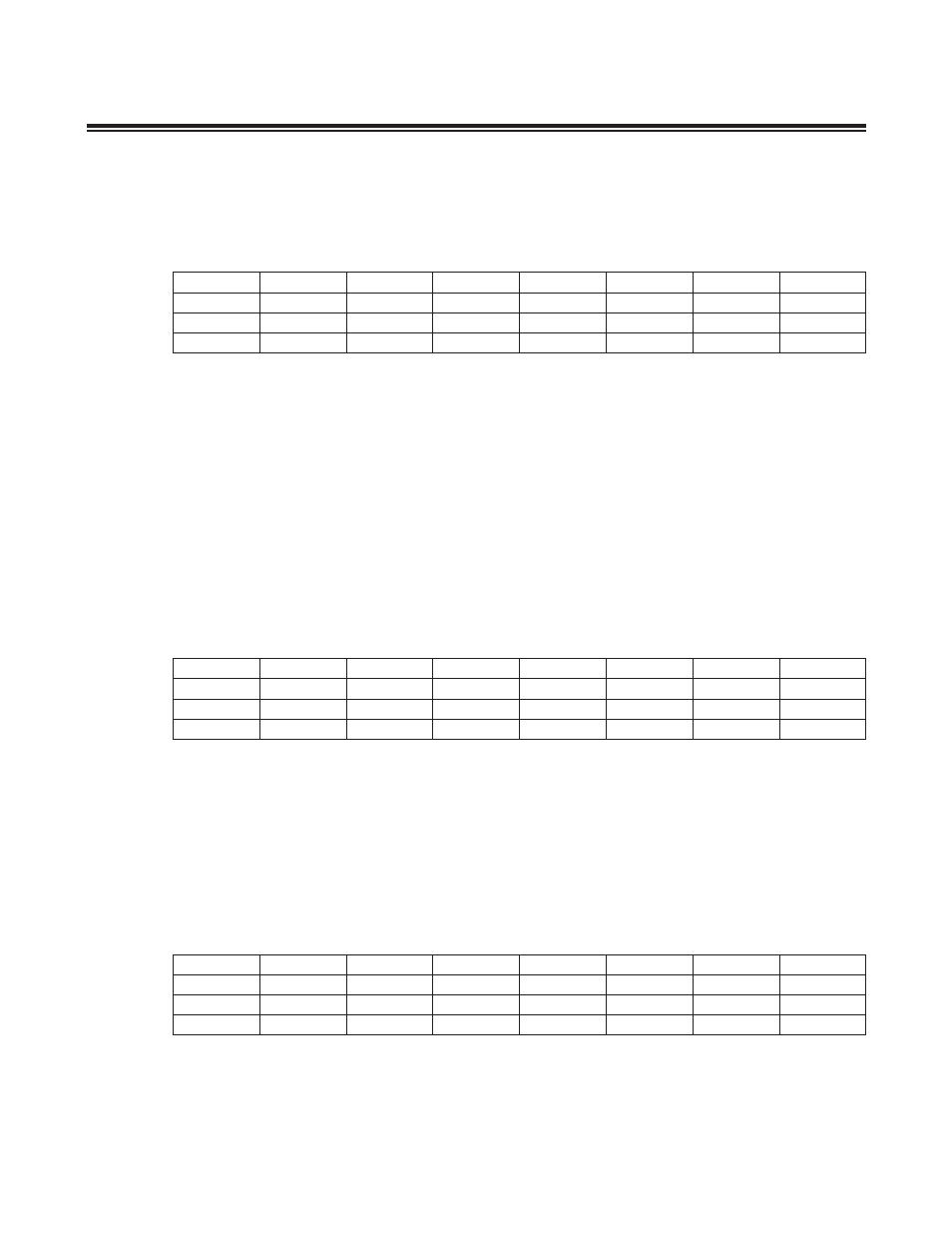

Register Name

EP0BC

Register Description

Endpoint 0 Byte Count Register

Register Address

UADDR[4:0] = 0Bh

Register Name

EP1BC

Register Description

Endpoint 1 OUT Byte Count Register

Register Address

UADDR[4:0] = 0Ch

Register Name

EP2BC

Register Description

Endpoint 2 IN Byte Count Register

Register Address

UADDR[4:0] = 0Dh

Bit #

7

6

5

4

3

2

1

0

Name

—

EP0BC6

EP0BC5

EP0BC4

EP0BC3

EP0BC2

EP0BC1

EP0BC0

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

Bit #

7

6

5

4

3

2

1

0

Name

—

EP1BC6

EP1BC5

EP1BC4

EP1BC3

EP1BC2

EP1BC1

EP1BC0

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

Bit #

7

6

5

4

3

2

1

0

Name

—

EP2BC6

EP2BC5

EP2BC4

EP2BC3

EP2BC2

EP2BC1

EP2BC0

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw