Table 4-3 . system register bit reset values -4, Table 4-3. system register bit reset values – Maxim Integrated MAXQ622 User Manual

Page 60

MAXQ612/MAXQ622 User’s Guide

4-4

Maxim Integrated

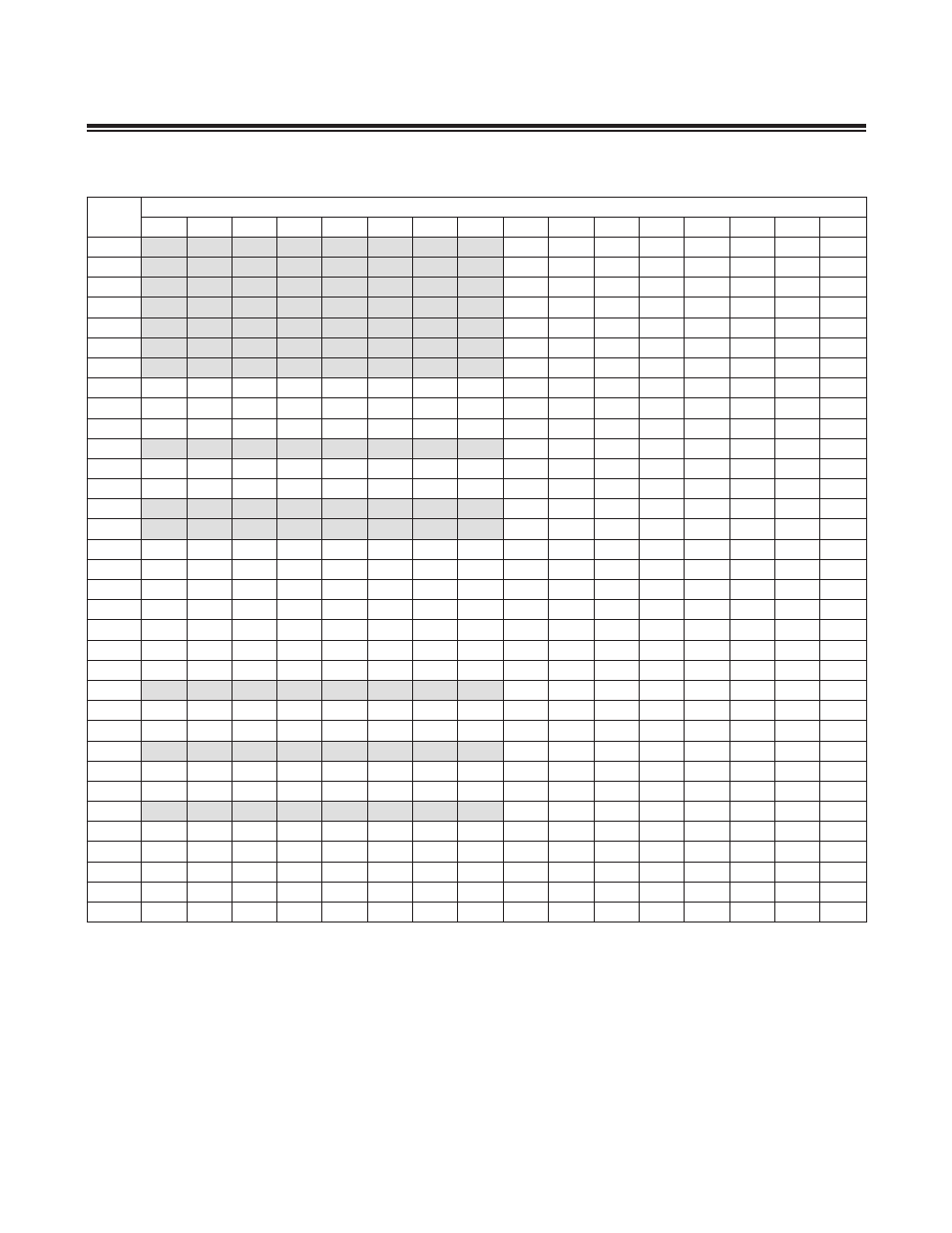

Table 4-3. System Register Bit Reset Values

Note 1: Bits marked as “s” are static across some or all resets.

Note 2: ULDR/UAPP reset values shown are for parts with 64KB/512B per page of program space. The reset value is the first

page address past the available program memory on all resets.

REG

BIT

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

AP

0

0

0

0

0

0

0

0

APC

0

0

0

0

0

0

0

0

PRIV

0

0

0

0

1

1

1

1

PRIVT0

0

0

0

0

0

0

0

0

PSF

1

0

0

0

0

0

0

0

IC

0

0

0

0

1

1

0

0

PRIVT1

0

0

0

0

0

0

0

0

SC

0

0

0

0

0

1

s

s

1

0

0

0

0

0

s

0

IPR0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

IPR1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

PRIVF

0

0

0

0

0

0

0

0

ULDR

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

UAPP

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

CKCN

s

s

s

0

0

0

0

0

WDCN

s

s

0

0

0

s

s

0

A[0:15]

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

PFX[0:7]

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

IP

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

SP

0

0

0

0

0

0

1

1

1

1

1

1

0

0

0

0

IV

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

LC[0]

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

LC[1]

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

OFFS

0

0

0

0

0

0

0

0

DPC

0

0

0

0

0

0

0

0

0

1

0

1

1

1

0

0

GR

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

GRL

0

0

0

0

0

0

0

0

BP

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

GRS

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

GRH

0

0

0

0

0

0

0

0

GRXL

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

FP

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

DP[0]

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

DP[1]

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

CP

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0