Figure 9-3 . usart mode 2 -6 – Maxim Integrated MAXQ622 User Manual

Page 142

MAXQ612/MAXQ622 User’s Guide

9-6

Maxim Integrated

Data is sampled in a similar fashion to mode 1 with the majority voting on three consecutive samples . Mode 2 uses

the sample divide-by-16 counter with either the clock divided by 2 or 4, thus resulting in a baud clock of either system

clock/32 or system clock/64 .

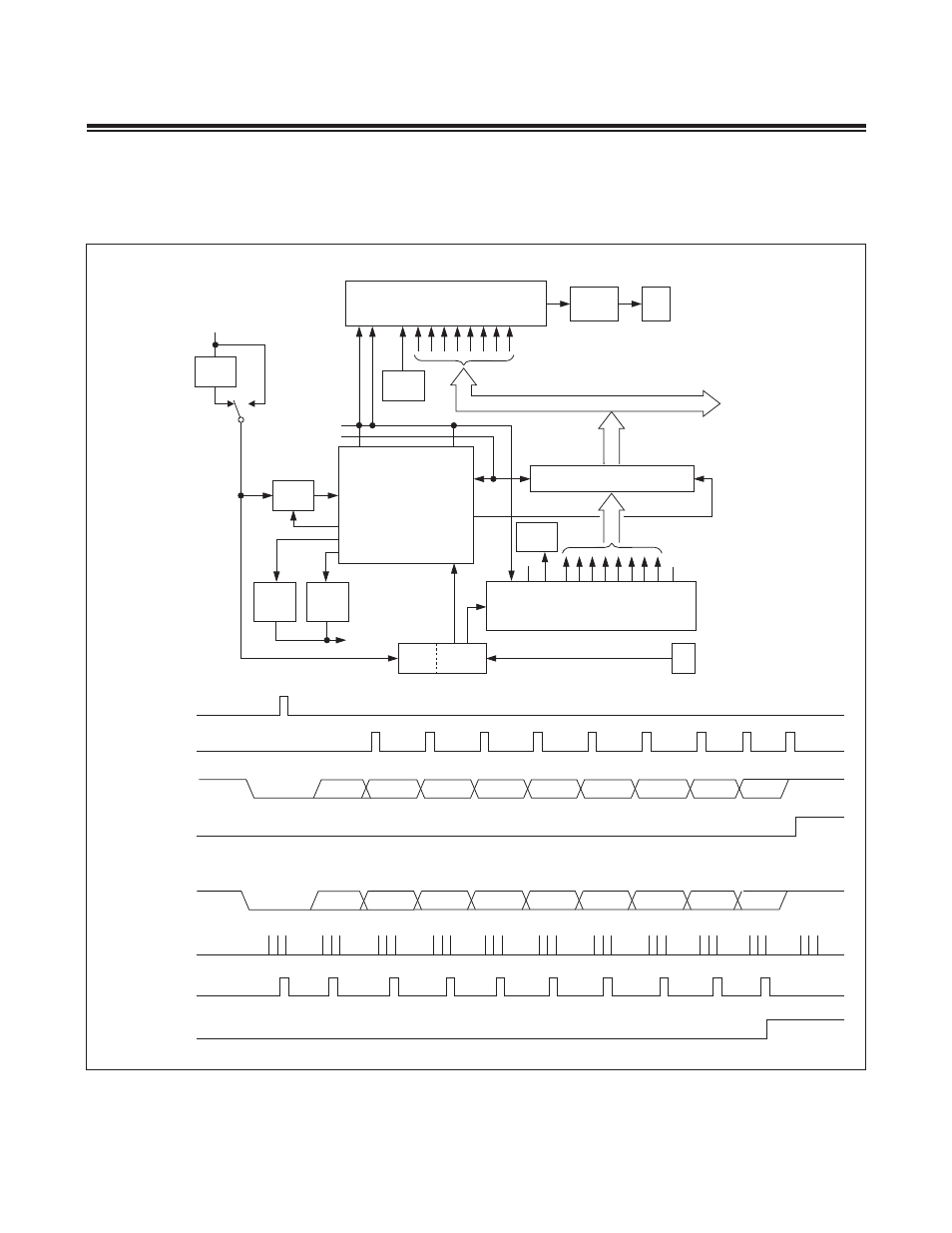

Figure 9-3. USART Mode 2

DIVIDE

BY 2

D7

D6

D5

D4

D3

D2 D1

D0

0

1

LOAD

CLOCK

TRANSMIT SHIFT REGISTER

S0

LATCH

RECEIVE DATA BUFFER

WR

SBUF

RD

D7

D6

D5

D4 D3 D2

D1

D0

CLOCK

RECEIVE SHIFT REGISTER

SI

RESET

SHIFT

CLOCK

LOAD

SERIAL

BUFFER

LOAD

SERIAL I/O

CONTROL

INTS

SHIFT

READ

SERIAL

BUFFER

TI

FLAG =

SCON.1

RI

FLAG =

SCON.0

DIVIDE

BY 16

LDSBUF

RDSBUF

0

1

SBUF

SMOD

RXD

PIN

SYSTEM

CLOCK/2

DIVIDE

BY 16

BIT

DETECTION

TXD

PIN

RB8 =

SCON.2

TB8 =

SCON.3

D8

START

STOP

D8

START

STOP

SERIAL

INTERRUPT

DATA BUS

D0

START

START

D1

D2

D3

D4

D5

D6

D7

RB8

STOP

D0

D1

D2

D3

D4

D5

D6

D7

TB8

STOP

RECEIVE TIMING

SHIFT

RI

RXD

BIT DETECTOR

SAMPLING

TRANSMIT TIMING

LDSBUF

SHIFT

TI

TXD