4 usb interrupt enable register (usbien), 5 usb interrupt register (usbint) – Maxim Integrated MAXQ622 User Manual

Page 177

MAXQ612/MAXQ622 User’s Guide

Maxim Integrated

12-7

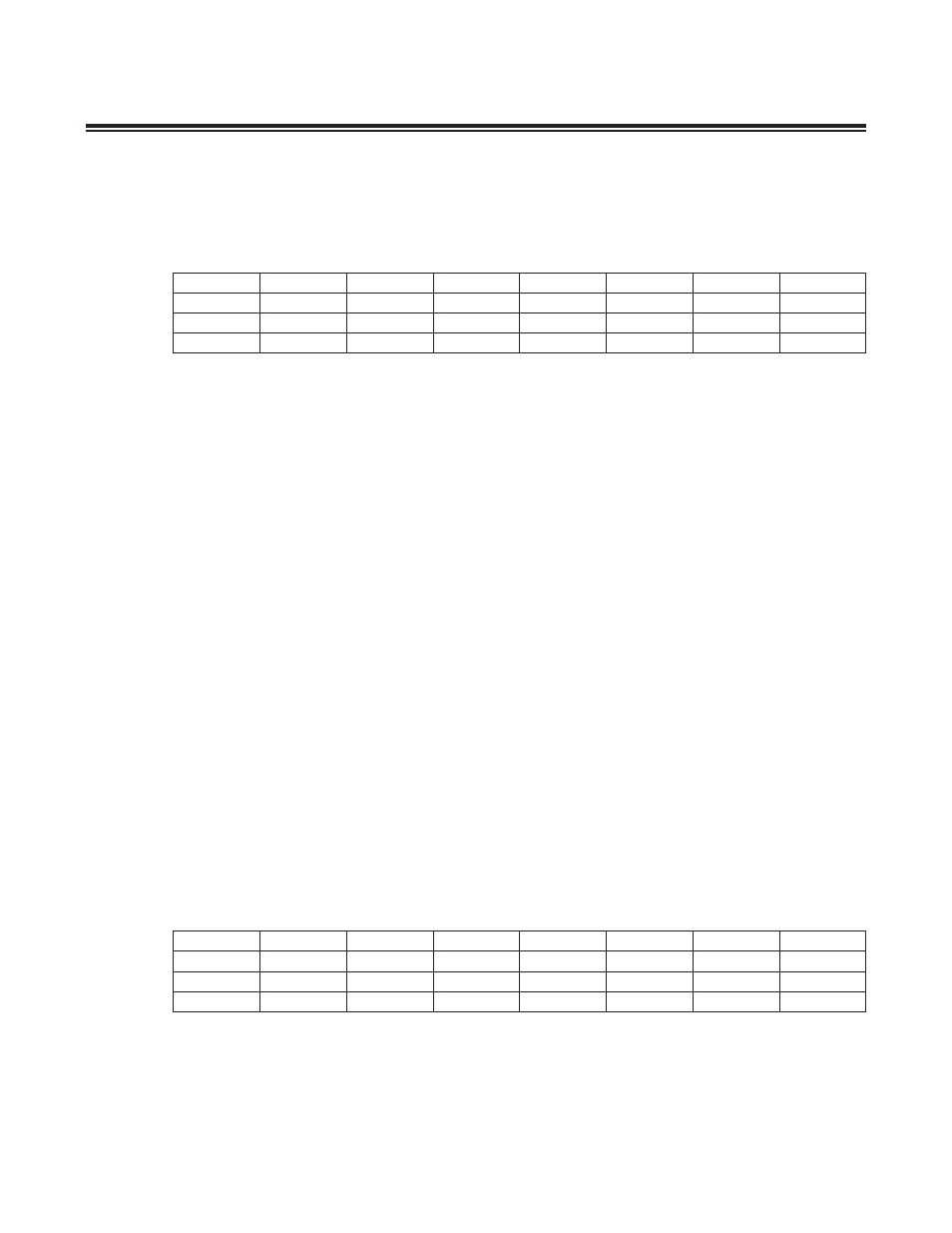

12.4.4 USB Interrupt Enable Register (USBIEN)

Note: This register is only accessible when USBEN = 1.

Note 1: This register is only accessible when USBEN = 1.

Note 2: Bit 3 is set on a bus reset.

All bits in this register except for USBIEN .3 and USBIEN .7 have a self-clearing mechanism that clears the interrupt

enable when a bus reset condition is detected .

Bit 7: USB Bus Reset Done Interrupt Enable (BRSTDNIE). Setting this bit to 1 causes an interrupt to the CPU when

a USB bus reset done condition is detected (BRSTDN = 1) . Clearing this bit to 0 disables the USB bus reset done

interrupt from generating . This bit holds the last value after bus rest .

Bit 6: VBUS Detect Interrupt Enable (VBUSIE). Setting this bit to 1 causes an interrupt to the CPU when the VBUS

presence condition is detected (VBUS = 1) . Clearing this bit to 0 disables the VBUS detect interrupt from generating .

Bit 5: No VBUS Interrupt Enable (NOVBUSIE). Setting this bit to 1 causes an interrupt to the CPU when the VBUS

absence condition is detected (NOVBUS = 1) . Clearing this bit to 0 disables the no VBUS interrupt from generating .

Bit 4: Suspend Interrupt Enable (SUSPIE). Setting this bit to 1 causes an interrupt to the CPU when a USB suspend

condition is detected (SUSP = 1) . Clearing this bit to 0 disables the USB suspend interrupt from generating .

Bit 3: USB Bus Reset Interrupt Enable (BRSTIE). Setting this bit to 1 causes an interrupt to the CPU when a USB

bus reset condition is detected (BRST = 1) . Clearing this bit to 0 disables the USB bus reset interrupt from generating .

This bit holds the last value after bus reset .

Bit 2: USB Bus Active Interrupt Enable (BACTIE). Setting this bit to 1 causes an interrupt to the CPU when there is

USB bus activity (BACT = 1) . Clearing this bit to 0 disables the bus activity interrupt from generating .

Bit 1: Remote Wake-Up Signaling Done Interrupt Enable (RWUDNIE). Setting this bit to 1 causes an interrupt to the

CPU when a USB remote wake-up signaling done condition is detected (RWUDN = 1) . Clearing this bit to 0 disables

the USB remote wake-up signaling done interrupt from generating .

Bit 0: D+ Activity Interrupt Enable (DPACTIE). Setting this bit to 1 causes an interrupt to the CPU when D+ activity

DPACTI is detected . Clearing this bit to 0 disables the DPACTI interrupt .

12.4.5 USB Interrupt Register (USBINT)

Bit 7: USB Bus Reset Done (BRSTDN). The BRSTDN bit indicates the end of a USB bus reset condition . This bit

remains set unless cleared by software . Setting this bit to 1 causes an interrupt to the CPU if USB bus reset done inter-

rupt is enabled (BRSTDNIE = 1) .

Register Name

USBIEN

Register Description

USB Interrupt Enable Register

Register Address

UADDR[4:0] = 04h

Register Name

USBINT

Register Description

USB Interrupt Register

Register Address

UADDR[4:0] = 05h

Bit #

7

6

5

4

3

2

1

0

Name

BRSTDNIE

VBUSIE

NOVBUSIE

SUSPIE

BRSTIE

BACTIE

RWUDNIE

DPACTIE

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

Bit #

7

6

5

4

3

2

1

0

Name

BRSTDN

VBUS

NOVBUS

SUSP

BRST

BACT

RWUDN

DPACT

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw