Table 14-1 . background mode commands -4, Table 14-1. background mode commands – Maxim Integrated MAXQ622 User Manual

Page 198

MAXQ612/MAXQ622 User’s Guide

14-4

Maxim Integrated

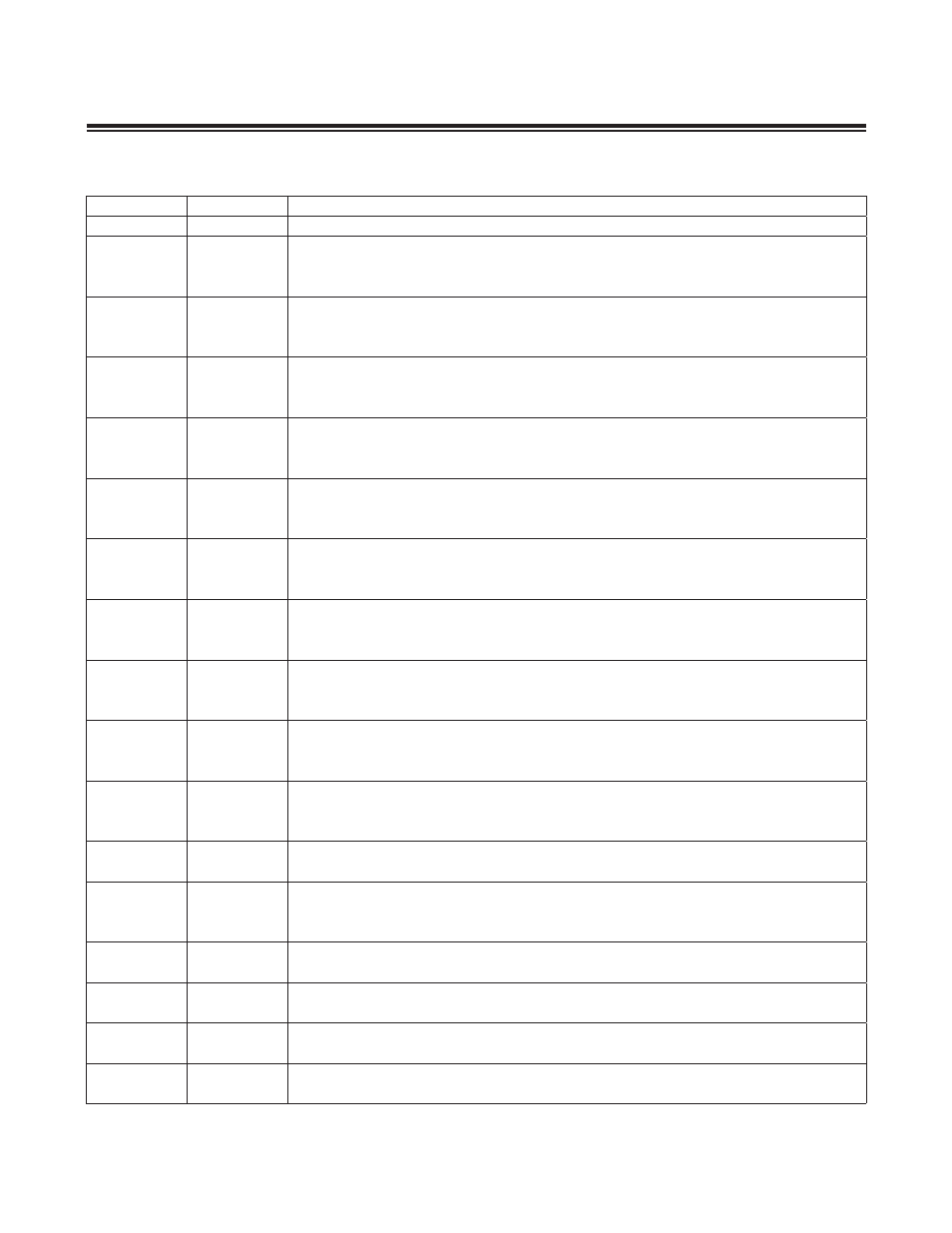

Table 14-1. Background Mode Commands

OP CODE

COMMAND

OPERATION

0000–0000

No Operation

No operation (default state for debug shift register) .

0000–0001

Read ICDC

Read control data from the ICDC . The contents of the ICDC register are loaded into the debug

shift register through the ICDB register for host read . This command requires one follow-on

transfer cycle .

0000–0010

Read ICDF

Read flags from the ICDF . The contents of the ICDF register (1 byte) are loaded into the debug

shift register through the ICDB register for host read . This command requires one follow-on

transfer cycle .

0000–0011

Read ICDA

Read data from the ICDA . The contents of the ICDA register are loaded into the debug shift

register through the ICDB register for host read . This command requires two follow-on transfer

cycles with the least significant byte first .

0000–0100

Read ICDD

Read data from the ICDD . The contents of the ICDD register are loaded into the debug shift

register through the ICDB register for host read . This command requires two follow-on transfer

cycles with the least significant byte first .

0000–0101

Read BP0

Read data from the BP0 . The contents of the BP0 register are loaded into the debug shift reg-

ister through the ICDB register for host read . This command requires two follow-on transfer

cycles with the least significant byte first .

0000–0110

Read BP1

Read data from the BP1 . The contents of the BP1 register are loaded into the debug shift reg-

ister through the ICDB register for host read . This command requires two follow-on transfer

cycles with the least significant byte first .

0000–0111

Read BP2

Read data from the BP2 . The contents of the BP2 register are loaded into the debug shift reg-

ister through the ICDB register for host read . This command requires two follow-on transfer

cycles with the least significant byte first .

0000–1000

Read BP3

Read data from the BP3 . The contents of the BP3 register are loaded into the debug shift reg-

ister through the ICDB register for host read . This command requires two follow-on transfer

cycles with the least significant byte first .

0000–1001

Read BP4

Read data from the BP4 . The contents of the BP4 register are loaded into the debug shift reg-

ister through the ICDB register for host read . This command requires two follow-on transfer

cycles with the least significant byte first .

0000–1010

Read BP5

Read data from the BP5 . The contents of the BP5 register are loaded into the debug shift reg-

ister through the ICDB register for host read . This command requires two follow-on transfer

cycles with the least significant byte first .

0001–0001

Write ICDC

Write control data to the ICDC . The contents of ICDB are loaded into the ICDC register by the

debug engine at the end of the data transfer cycle .

0001–0011

Write ICDA

Write data to the ICDA . The contents of ICDB are loaded into the ICDA register by the debug

engine at the end of the data transfer cycles . Data is transferred with the least significant byte

first .

0001–0100

Write ICDD

Write data to the ICDD . The contents of ICDB are loaded into the ICDD register by the debug

engine at the end of data transfer cycles . Data is transferred with the least significant byte first .

0001–0101

Write BP0

Write data to the BP0 . The contents of ICDB are loaded into the BP0 register by the debug

engine at the end of data transfer cycles . Data is transferred with the least significant byte first .

0001–0110

Write BP1

Write data to the BP1 . The contents of ICDB are loaded into the BP1 register by the debug

engine at the end of data transfer cycles . Data is transferred with the least significant byte first .

0001–0111

Write BP2

Write data to the BP2 . The contents of ICDB are loaded into the BP2 register by the debug

engine at the end of data transfer cycles . Data is transferred with the least significant byte first .