Maxim Integrated MAXQ622 User Manual

Page 7

MAXQ612/MAXQ622 User’s Guide

Maxim Integrated

2-3

SECTION 2: ARCHITECTURE

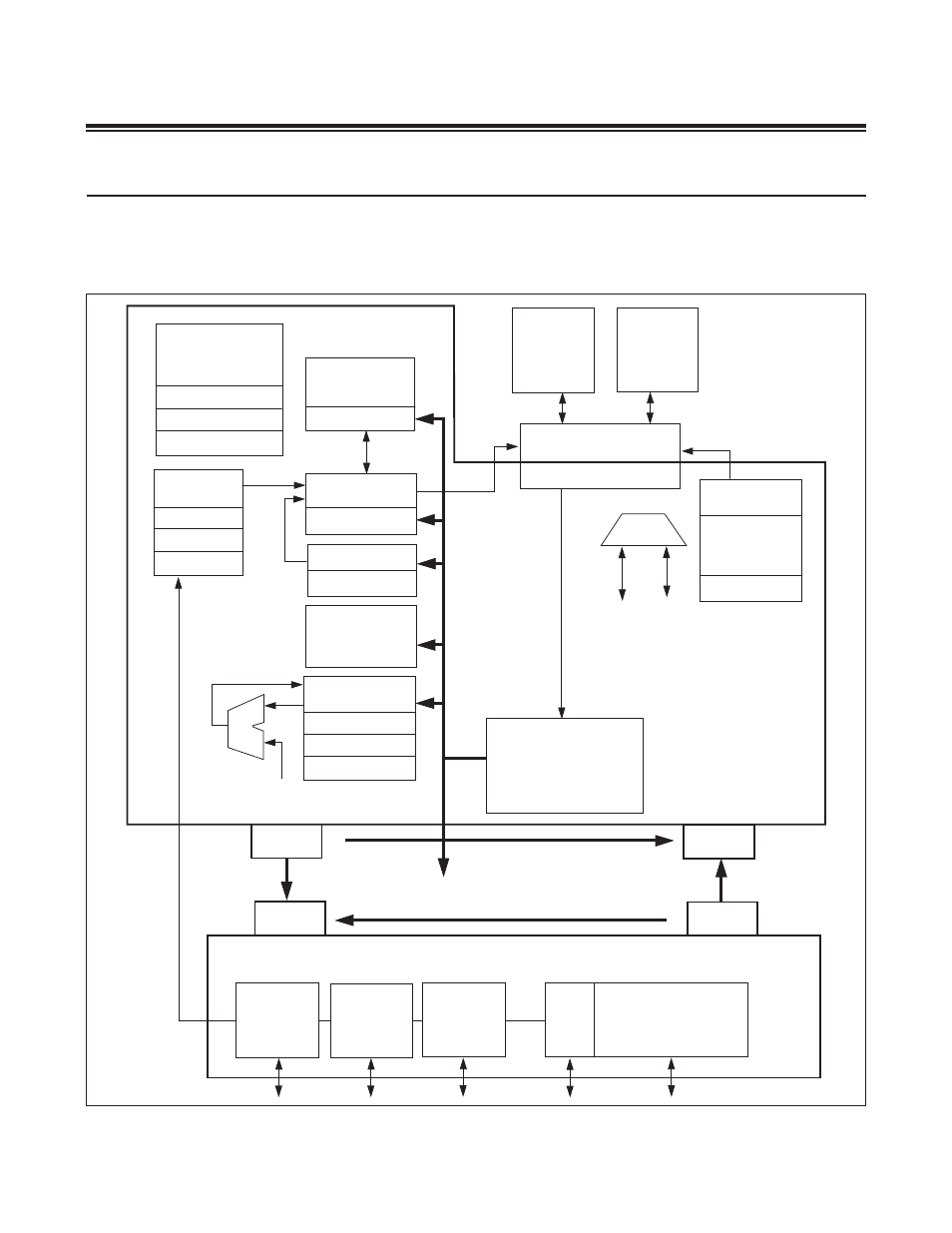

The MAXQ612/MAXQ622 are designed to be modular and expandable . Top-level instruction decoding is extremely

simple and based on transfers to and from registers . The registers are organized into functional modules, which are

in turn divided into the system register and peripheral register groups . Figure 2-1 illustrates the modular architecture

and the basic transport possibilities .

Figure 2-1. MAXQ612/MAXQ622 Transport-Triggered Architecture

SYSTEM MODULES/

REGISTERS

PERIPHERAL MODULES/REGISTERS

DATA

MEMORY

dst

ADDITIONAL MODULES

FOR FUTURE EXPANSION

STACK

MEMORY

CKCN

WDCN

IC

ADDRESS

GENERATION

IP

SP

IC

LOOP COUNTERS

LC[n]

IPR0

IV

INTERRUPT

LOGIC

CLOCK CONTROL,

WATCHDOG TIMER

AND POWER MONITOR

BOOLEAN

VARIABLE

MANIPULATION

ACCUMULATORS

(16)

AP

APC

PSF

INSTRUCTION

DECODE

(src, dst TRANSPORT

DETERMINATION)

MUX

DATA POINTERS

DP[0], DP[1]

FP =

(BP + OFFS)

DPC

SC

MEMORY MANAGEMENT

UNIT (MMU)

PROGRAM

MEMORY

src

dst

src

GENERAL-

PURPOSE

I/O

USB

TIMERS/

COUNTERS

USART,

SPI,

I

2

C