8 endpoint stall register (epstl), 12 .4 .8 endpoint stall register (epstl) -10 – Maxim Integrated MAXQ622 User Manual

Page 180

MAXQ612/MAXQ622 User’s Guide

12-10

Maxim Integrated

12.4.8 Endpoint Stall Register (EPSTL)

Bit 7: Reserved. Reads returns zero.

Bit 6: Acknowledge Status Stage (ACKSTAT). When this bit is set to 1, the SIE responds to the host with an ACK

handshake in the status stage of control transfer . Until the CPU either acknowledges (ACKSTAT = 1) or stalls the trans-

fer, the SIE answers the status stage of the control transfer with the NAK handshake . This bit is cleared after the SIE

sends an ACK handshake in the status stage of a control transfer, new setup packet has been detected, or the stall

bit(s) is set . This bit can also be cleared by CPU writing a 0 .

Bit 5: Stall Status Stage (STLSTAT). The stall status stage bit, together with the ACKSTAT bit, indicates to the SIE how

to respond in the status stage of a control transfer . When this bit is cleared to 0, the ACKSTAT bit controls the status

stage of a control transfer . When this bit is set to 1, the SIE always sends a stall response to the host in response to

a control transfer . Until the CPU either acknowledges (ACKSTAT = 1) or stalls the transfer, the SIE answers the status

stage of a control transfer with the NAK handshake . This bit remains set unless cleared by software . This bit is auto-

matically cleared upon the arrival of a setup token .

Bit 4: EP3-IN Stall (STLEP3). If set to 1, the SIE returns a stall handshake for an IN request directed to EP3 regardless

of the status of the other control bits . This bit remains set unless cleared by software .

Bit 3: EP2-IN Stall (STLEP2). If set to 1, the SIE returns a stall handshake for an IN request directed to EP2 regardless

of the status of the other control bits . This bit remains set unless cleared by software .

Bit 2: EP1-OUT Stall (STLEP1). If set to 1, the SIE returns a stall handshake for an OUT request directed to EP1

regardless of the status of the other control bits . This bit remains set unless cleared by software .

Bit 1: EP0-OUT Stall (STLOUT0). If set to 1, the SIE returns a stall handshake for an OUT request directed to EP0

regardless of the status of the other control bits . This bit remains set unless cleared by software . This bit is automati-

cally cleared upon the arrival of a setup token .

Bit 0: EP0-IN Stall (STLIN0). If set to 1, the SIE returns a stall handshake for an IN request directed to EP0 regardless

of the status of the other control bits . This bit remains set unless cleared by software . This bit is automatically cleared

upon the arrival of a setup token .

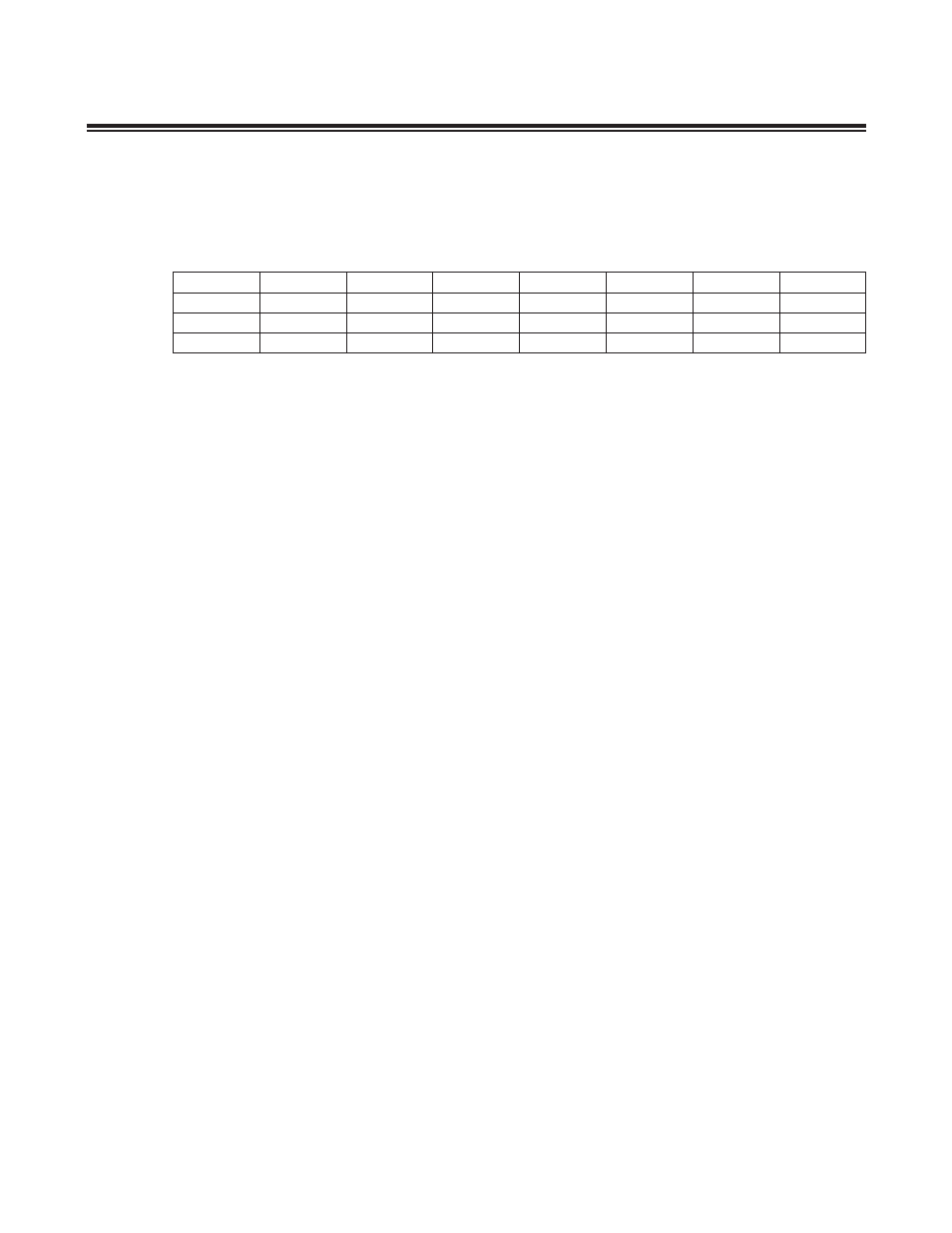

Register Name

EPSTL

Register Description

Endpoint Stall Register

Register Address

UADDR[4:0] = 08h

Bit #

7

6

5

4

3

2

1

0

Name

—

ACKSTAT

STLSTAT

STLEP3

STLEP2

STLEP1

STLOUT0

STLIN0

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw