4 i2c peripheral register descriptions, 1 i2c control register (i2ccn), 11 .4 i – Maxim Integrated MAXQ622 User Manual

Page 163: C peripheral register descriptions -8, 11 .4 .1 i, C control register (i2ccn) -8, C peripheral register descriptions, C control register (i2ccn)

MAXQ612/MAXQ622 User’s Guide

11-8

Maxim Integrated

11.4 I

2

C Peripheral Register Descriptions

The following peripheral registers are used to control the integrated I

2

C peripheral on the devices .

11.4.1 I

2

C Control Register (I2CCN)

Bit 15: I

2

C Reset (I2CRST). Setting this bit to 1 aborts the current transaction and resets the I

2

C controller . This bit is

set to 1 by software and is only cleared to 0 by hardware after the reset or when I2CEN = 0 .

Bits 14 to 10 and 3: Reserved. Reads returns 0.

Bit 9: I

2

C Clock Stretch Enable (I2CSTREN). Setting this bit to 1 stretches the clock (holds SCL low) at the end of the

clock cycle specified in I2CSTRS . Clearing this bit disables clock stretching .

Bit 8: I

2

C General Call Enable (I2CGCEN). Setting this bit to 1 enables the I

2

C to respond to a general call address

(address = 0000 0000) . Clearing this bit to 0 disables the I

2

C to respond to a general call address .

Bit 7: I

2

C STOP Enable (I2CSTOP). Setting this bit to 1 generates a STOP condition . This bit is automatically self-

cleared to 0 after the STOP condition has been generated . In master mode, setting this bit can also start the timeout

timer if enabled . If the timeout timer expires before the STOP condition can be generated, a timeout interrupt is gener-

ated to the CPU if enabled . The I2CSTOP bit is also cleared to 0 by the timeout event .

Note that this bit has no effect when the I

2

C is operating in slave mode (I2CMST = 0) and is reset to 0 when I2CMST

= 0 or I2CEN = 0 . Setting the I2CSTOP bit to 1 while I2CSTART = 1 is an invalid operation and is ignored, leaving the

I2CSTOP bit cleared to 0 .

Bit 6: I

2

C START (I2CSTART). Setting this bit automatically generates a START condition when the bus is free or a

repeated START condition during a transfer where the I

2

C module is operating as the master . This bit is automati-

cally self-cleared to 0 after the START condition has been generated . If the I

2

C START interrupt is enabled, a START

condition generates an interrupt to the CPU . In master mode, setting this bit also starts the timeout timer if enabled . If

the timeout timer expires before the START condition can be generated, a timeout interrupt is generated to the CPU if

enabled . The I2CSTART bit is also cleared to 0 by the timeout event .

Note that this bit has no effect when the I

2

C is operating in slave mode (I2CMST = 0) and is reset to 0 when I2CMST

= 0 or I2CEN = 0 . Also, the I2CSTART and I2CSTOP bits are mutually exclusive . If both bits are set at the same time,

it is considered as an invalid operation and the I

2

C controller ignores the request and resets both bits to 0 . Setting the

I2CSTART bit to 1 while I2CSTOP = 1 is an invalid operation and is ignored, leaving the I2CSTART bit cleared to 0 .

Note 1: I2CSTART and I2CSTOP are mutually exclusive and reset to 0 when I2CMST = 0 or I2CEN = 0.

Note 2: I2CRST is reset to 0 when I2CEN = 0.

Note 3: Writes to I2CMST, I2CMODE, and I2CEN are ignored when I2CBUSY = 1.

Note 4: If I2CRST = 1, I2CEN can be written when I2CBUSY = 1.

Note 5: Writes to I2CACK are ignored if I2RST = 1.

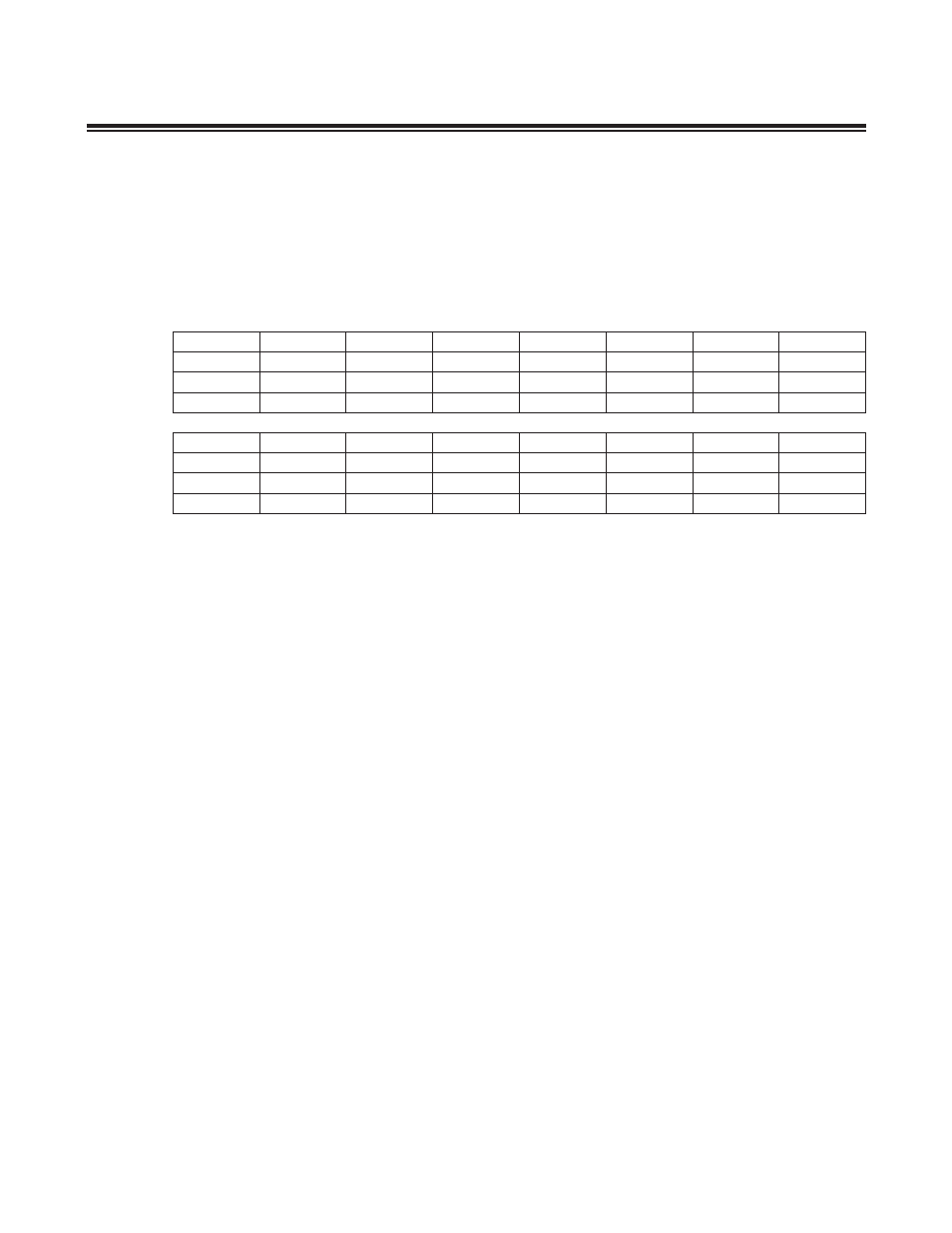

Register Name

I2CCN

Register Description

I

2

C Control Register

Register Address

M4[00h]

Bit #

15

14

13

12

11

10

9

8

Name

I2CRST

—

—

—

—

—

I2CSTREN

I2CGCEN

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

Bit #

7

6

5

4

3

2

1

0

Name

I2CSTOP

I2CSTART

I2CACK

I2CSTRS

—

I2CMODE

I2CMST

I2CEN

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw