Maxim Integrated MAXQ622 User Manual

Page 76

MAXQ612/MAXQ622 User’s Guide

Maxim Integrated

5-3

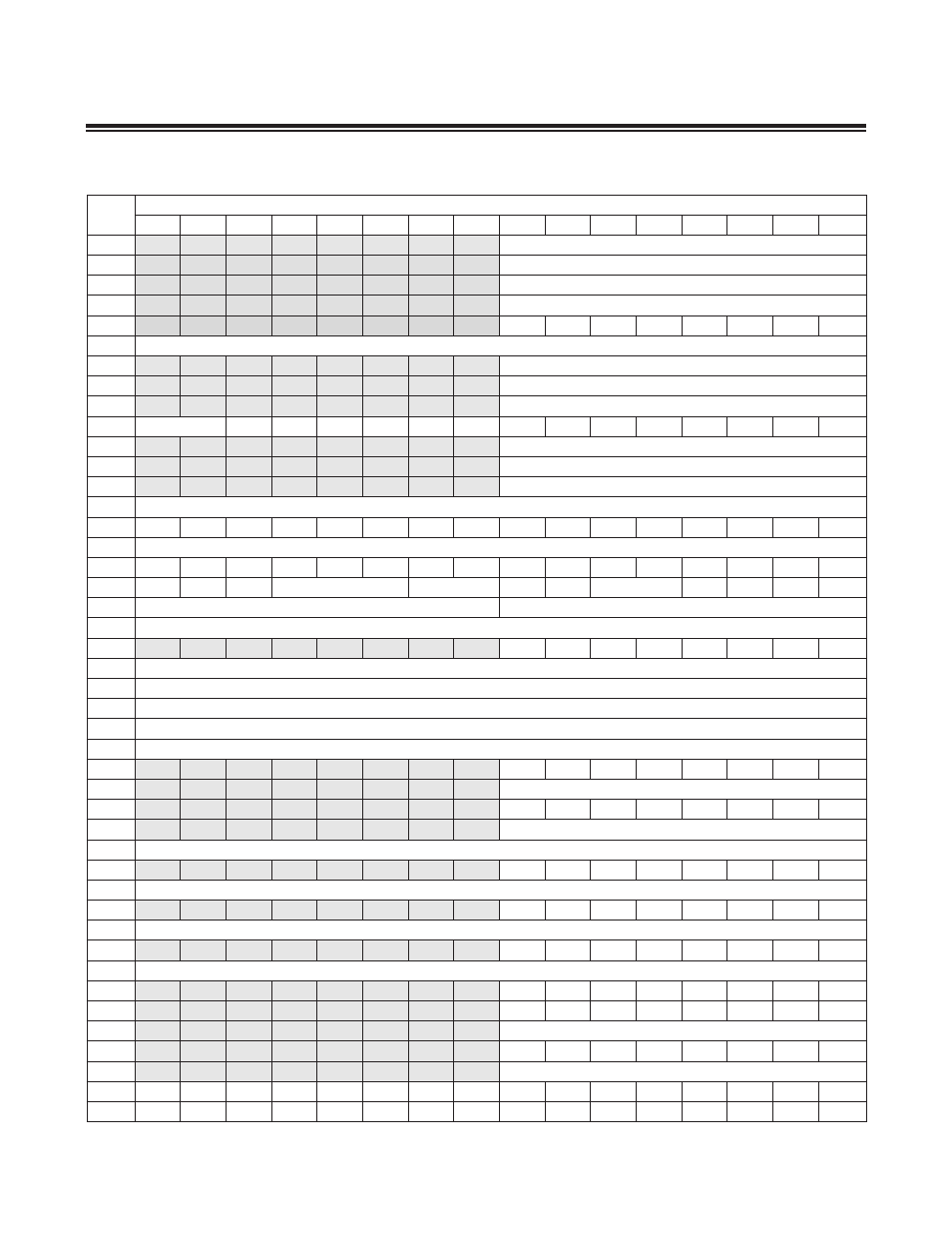

Table 5-2. Peripheral Register Bit Function (continued)

REG

BIT

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

CHPREV

CHPREV[7:0]

PO4

PO4[7:0]

PO5

PO5[7:0]

PO6

PO6[7:0]

WUTC

—

—

—

—

—

—

WTF

WTE

WUT

WUT[15:0]

PI4

PI4[7:0]

PI5

PI5[7:0]

PI6

PI6[7:0]

PWCN PFWARNCN[1:0] CKRY

CTM

CTMS FRCVDD PFRCK1 PFRCK0 PFRST IRRXWP IRTXOUT IRTXOE REGEN

PFI

PFIE

PFD

PD4

PD4[7:0]

PD5

PD5[7:0]

PD6

PD6[7:0]

TB0R

TB0R[15:0]

TB0CN

C/TB

—

—

TBCS

TBCR

TBPS2 TBPS1 TBPS0

TFB

EXFB

TBOE

DCEN

EXENB

TRB

ETB

CP/RLB

TB1R

TB1R[15:0]

TB1CN

C/TB

—

—

TBCS

TBCR

TBPS2 TBPS1 TBPS0

TFB

EXFB

TBOE

DCEN

EXENB

TRB

ETB

CP/RLB

IRCN

—

—

—

IRDIV[2:0]

IRENV[1:0]

IRXRL

IRCFME

IRRXSEL[1:0]

IRDATA IRTXPOL IRMODE

IREN

IRCA

IRCAH[7:0]

IRCAL[7:0]

IRMT

IRMT[15:0]

IRCNB

—

—

—

—

RXBCNT

IRIE

IRIF

IROV

TB0C

TB0C[15:0]

TB0V

TB0V[15:0]

TB1C

TB1C[15:0]

TB1V

TB1V[15:0]

IRV

IRV[15:0]

SCON0

SM0/FE

SM1

SM2

REN

TB8

RB8

TI

RI

SBUF0

SBUF0[7:0]

SCON1

SM0/FE

SM1

SM2

REN

TB8

RB8

TI

RI

SBUF1

SBUF1[7:0]

SPIB0

SPIB0[15:0]

SPICN0

STBY

SPIC

ROVR

WCOL

MODF

MODFE

MSTM

SPIEN

SPIB1

SPIB1[15:0]

SPICN1

STBY

SPIC

ROVR

WCOL

MODF

MODFE

MSTM

SPIEN

PR0

PR0[15:0]

SMD0

—

—

—

—

—

ESI0

SMOD0

FEDE0

PR1

PR1[15:0]

SMD1

—

—

—

—

—

ESI1

SMOD1

FEDE1

SPICF0

ESPII

SAS

—

—

—

CHR

CKPHA CKPOL

SPICK0

CKR[7:0]

SPICF1

ESPII

SAS

—

—

—

CHR

CKPHA CKPOL

SPICK1

CKR[7:0]

I2CCN I2CRST

—

—

—

—

—

I2CSTREN I2CGCEN I2CSTOP I2CSTART I2CACK I2CSTRS

—

I2CMODE I2CMST

I2CEN

I2CST

I2CBUS I2CBUSY

—

—

I2CSPI

I2CSCL

I2CROI

I2CGCI I2CNACKI I2CALI

I2CAMI

I2CTOI

I2CSTRI

I2CRXI

I2CTXI

I2CSRI