18 endpoint 3 buffer register (ep3buf), 19 setup data buffer register (sudbuf) – Maxim Integrated MAXQ622 User Manual

Page 185

MAXQ612/MAXQ622 User’s Guide

Maxim Integrated

12-15

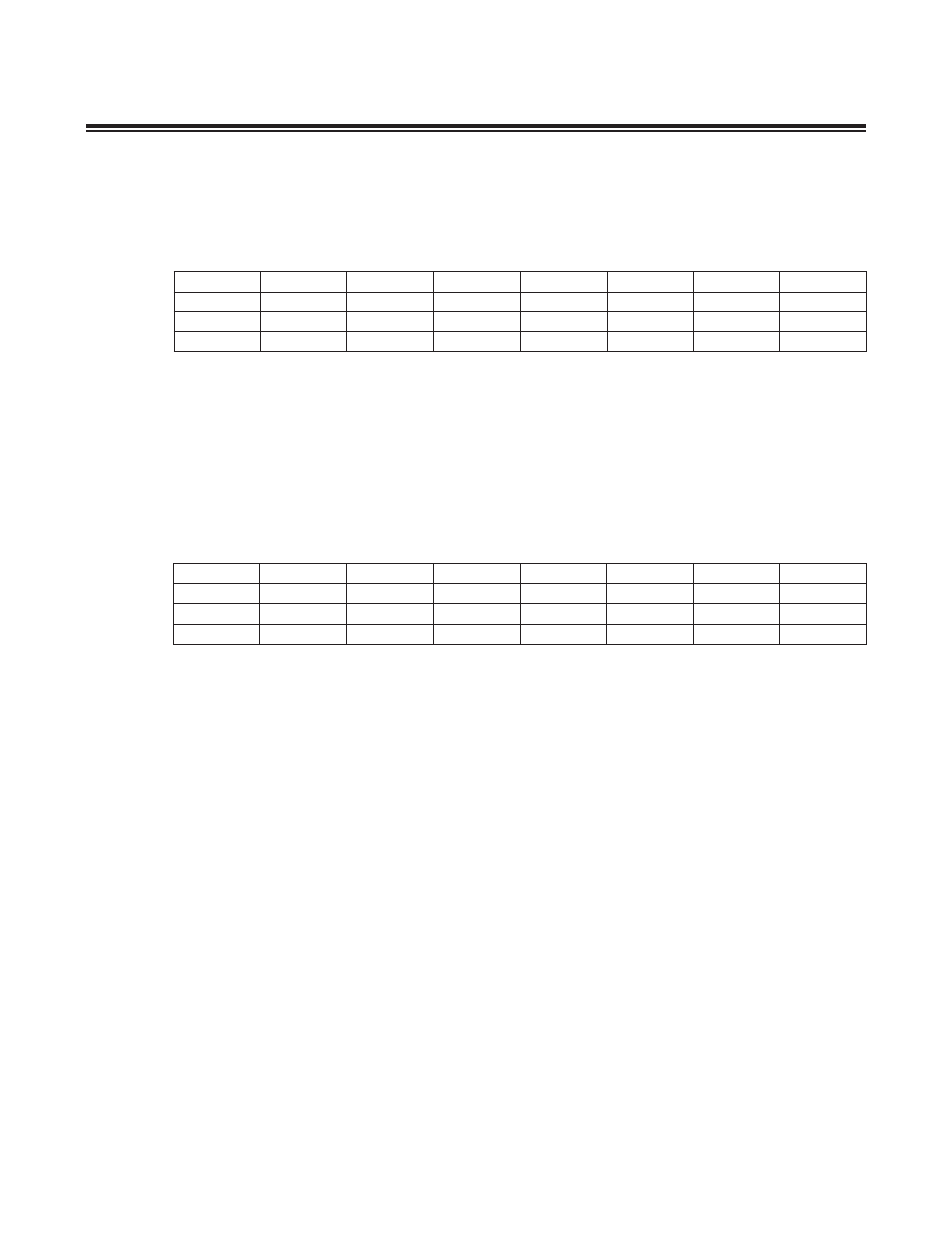

12.4.18 Endpoint 3 Buffer Register (EP3BUF)

Note: This register is indetermistic on POR and retains its value on all other forms of reset.

Note: This register is indetermistic on POR and retains its value on all other forms of reset.

Bits 7 to 0: EP3 Buffer (EP3BUF[7:0]). These data register bits are used for supplying data to the 64-byte EP3-IN

buffer . The CPU loads bytes into the EP3BUF buffer in preparation for sending to the host . The SIE sends these bytes

over USB in response to an IN request to EP3-IN .

12.4.19 Setup Data Buffer Register (SUDBUF)

Bits 7 to 0: Setup Data Buffer (SUDBUF[7:0]). These data register bits are used for reading data from the 8-byte

setup buffer . The SIE fills the setup buffer with SETUP bytes transmitted from the host . After successfully receiving the

SETUP transfer, the SIE ACKs the transfer and asserts the SUDAV interrupt request . When the CPU receives an SUDAV

interrupt request, it reads 8 bytes of data from this register .

Register Name

SUDBUF

Register Description

Setup Data Buffer Register

Register Address

UADDR[4:0] = 14h

Register Name

EP3BUF

Register Description

Endpoint 3 Buffer Register

Register Address

UADDR[4:0] = 13h

Bit #

7

6

5

4

3

2

1

0

Name

SUDBUF7

SUDBUF6

SUDBUF5

SUDBUF4

SUDBUF3

SUDBUF2

SUDBUF1

SUDBUF0

Reset

s

s

s

s

s

s

s

s

Access

rw

rw

rw

rw

rw

rw

rw

rw

Bit #

7

6

5

4

3

2

1

0

Name

EP3BUF7

EP3BUF6

EP3BUF5

EP3BUF4

EP3BUF3

EP3BUF2

EP3BUF1

EP3BUF0

Reset

s

s

s

s

s

s

s

s

Access

rw

rw

rw

rw

rw

rw

rw

rw