Status flags – Rockwell Automation 1769-HSC Compact High Speed Counter Module User Manual

Page 106

106

Rockwell Automation Publication 1769-UM006E-EN-P - July 2013

Chapter 4

Module Configuration, Output, and Input Data

Status Flags

The status bits for the counter (

n) are described below.

COvf - Count Overflow (Ctr[0].Overflow to Ctr[3].Overflow)

For linear counters, this bit is set when the counter is, or has been, in an overflow

condition. For ring counters, this bit is set when the counter has rolled over.

COvf is reset when the Ctr

nResetCountOverflow bit transitions from 0 to 1.

for more information about linear and ring

counters.

CUdf - Count Underflow (Ctr[0].Underflow to Ctr[3].Underflow)

For linear counters, this bit is set when the counter is, or has been, in an

underflow condition. For ring counters, this bit is set when the counter has rolled

under. CUdf is reset when the Ctr

nResetCountUnderflow bit transitions from

0 to 1.

for more information about linear and ring

counters.

REZ - Rising Edge Z (Ctr[0].RisingEdgeZ to Ctr[1].RisingEdgeZ)

This bit is set (1) when Z

n, as modified by the CtrnZInvert and CtrnZInhibit

bits, has a rising edge. It is reset (0) by a 0 to 1 transition of the

Ctr

nResetRisingEdgeZ bit in the output array. N is equal to 0 or 1 depending

upon which input is used, Z0 or Z1.

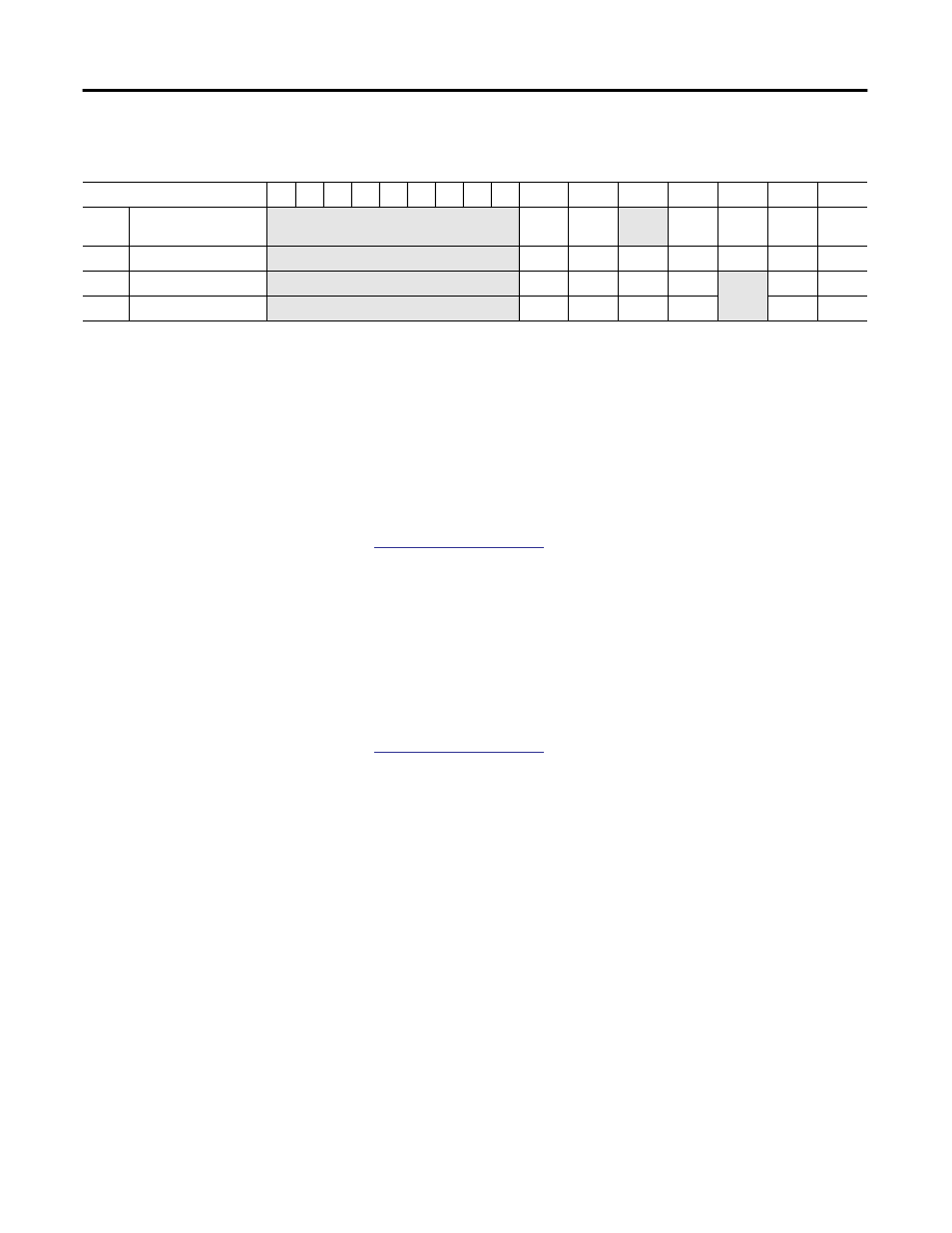

Input Array Words

15

14

13

12

11

10

09

08

07

06

05

(1)

04

03

02

01

00

12

Counter 0 Status Flags

Not used

C0PW

RV

Not

used

IDW

REZ

CUdf

COvf

22

Counter 1 Status Flags

Not used

C1PW

RV

IC

IDW

REZ

CUdf

COvf

28

Counter 2 Status Flags

Not used

C2PW

RV

IC

IDW

Not

used

CUdf

COvf

34

Counter 3 Status Flags

Not used

C3PW

RV

IC

IDW

CUdf

COvf

(1) Bit 05 is not used for the packaged controller.