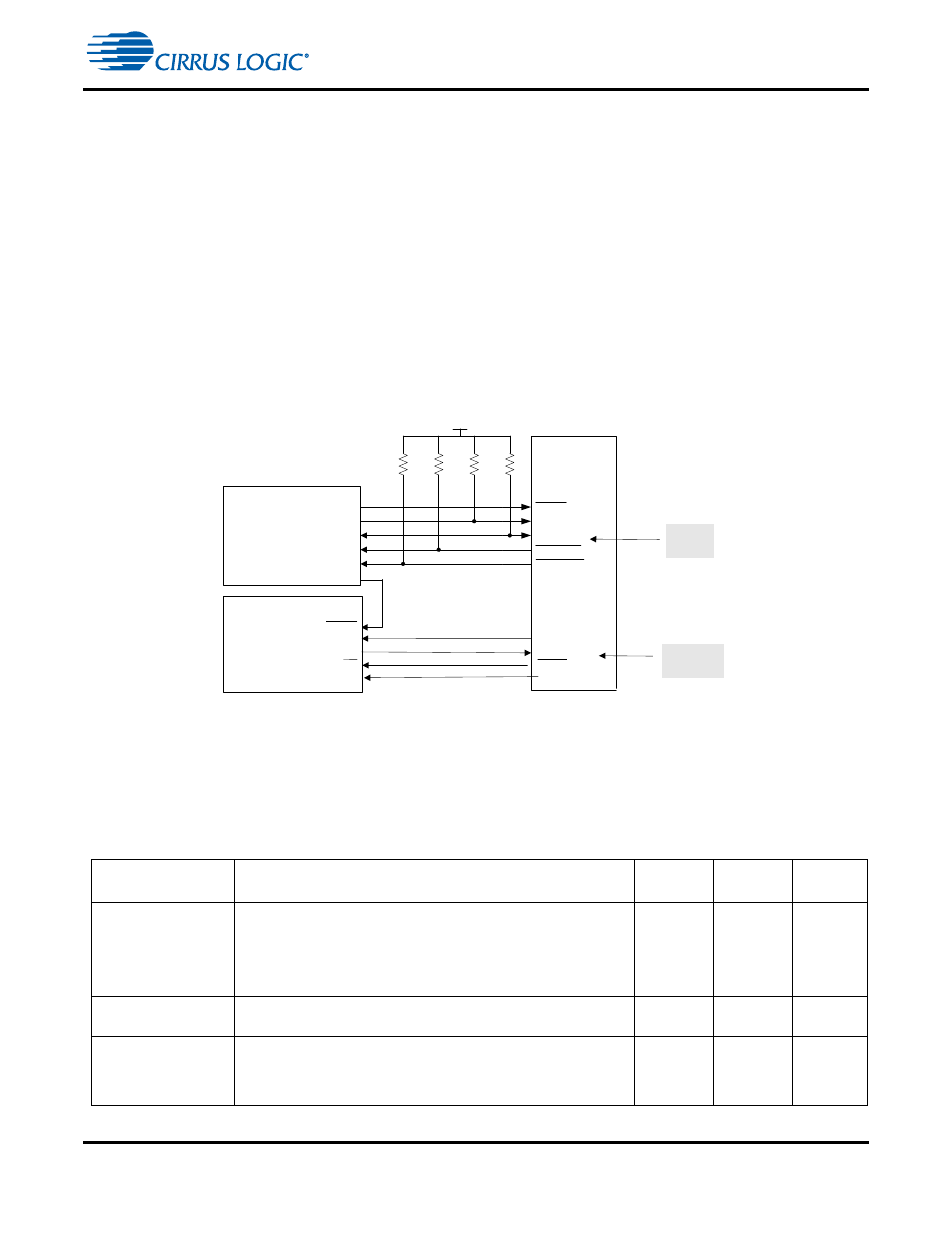

1 i2c system bus description, Figure 2-8. block diagram of i2c system bus -10, Table 2-2. serial control port 1 i2c signals -10 – Cirrus Logic CS4970x4 User Manual

Page 56: C system bus description

I2C Port

CS4953x4/CS4970x4 System Designer’s Guide

DS810UM6

Copyright 2013 Cirrus Logic, Inc

2-10

2.5.1 I

2

C System Bus Description

Devices can be considered Masters or Slaves when performing data transfers. A Master is the device

which initiates a data transfer on the bus and generates the clock signals to permit that transfer. Any

device addressed by the initiator is considered a Slave.

The CS4953x4/CS4970x4 has two serial ports. The O/S currently supports only Slave mode host

communication on SCP1, and Master mode communication on SCP2 for booting from a SPI Flash.

Both SCP1_SDA and SCP1_CLK are bidirectional lines. When the bus is free, both lines are pulled high

by resistors. The output stages of devices connected to the bus must have an open-drain or open-

collector to perform the wired-AND function.

As seen in

, two serial ports are available on the CS4953x4/CS4970x4. SCP1 is configured as

Slave and SCP2 is configured as a Master. SCP2 is used only in systems that are booting from SPI Flash.

Figure 2-8. Block Diagram of I

2

C System Bus

shows the signal names, descriptions, and pin number of the signals associated with the I

2

C

Serial Control Port on the CS4953x4/CS4970x4.

Table 2-2. Serial Control Port 1 I

2

C Signals

Pin Name

Pin Description

LQFP-144

Pin #

LQFP-128

Pin #

Pin

Type

SCP1_CLK

I

2

C Control Port Bit Clock.

In Master mode, this pin serves as the serial control clock output (open

drain in I

2

C mode / output in SPI mode). In serial Slave mode, this pin

serves as the serial control clock input. In I

2

C Slave mode the clock can

be pulled low by the port to stall the Master.

99

126

Open Drain

SCP1_SDA

Bidirectional Data I

2

C Mode Master/Slave Data IO. In I

2

C Master and

Slave mode, this open drain pin serves as the data input and output.

97

124

Open Drain

SCP1_IRQ

Control Port Data Ready Interrupt Request, Output, Active Low

This pin is driven low when the DSP has a message for the host to read.

The pin will go high when the host has read the message and the DSP

has no further messages.

100

4

Open Drain

System Microcontroller

RESET

SCP1_CLK

SCP1_SDA

SCP1_IRQ

SCP1_BSY

CS4970x4/

CS4954x4

3.3k

3.3k

3.3V

3.3k

3.3k

SLAVE

ONLY

SPI Flash

MOSI

MISO

CS

CLK

SCP2_CLK

SCP2_MOSI

SCP2_MISO

EE_CS

MASTER

ONLY

RESET