AMD SB600 User Manual

Page 99

©2008 Advanced Micro Devices, Inc.

SMBus Module and ACPI Block (Device 20, Function 0)

AMD SB600 Register Reference Manual

Proprietary

Page 99

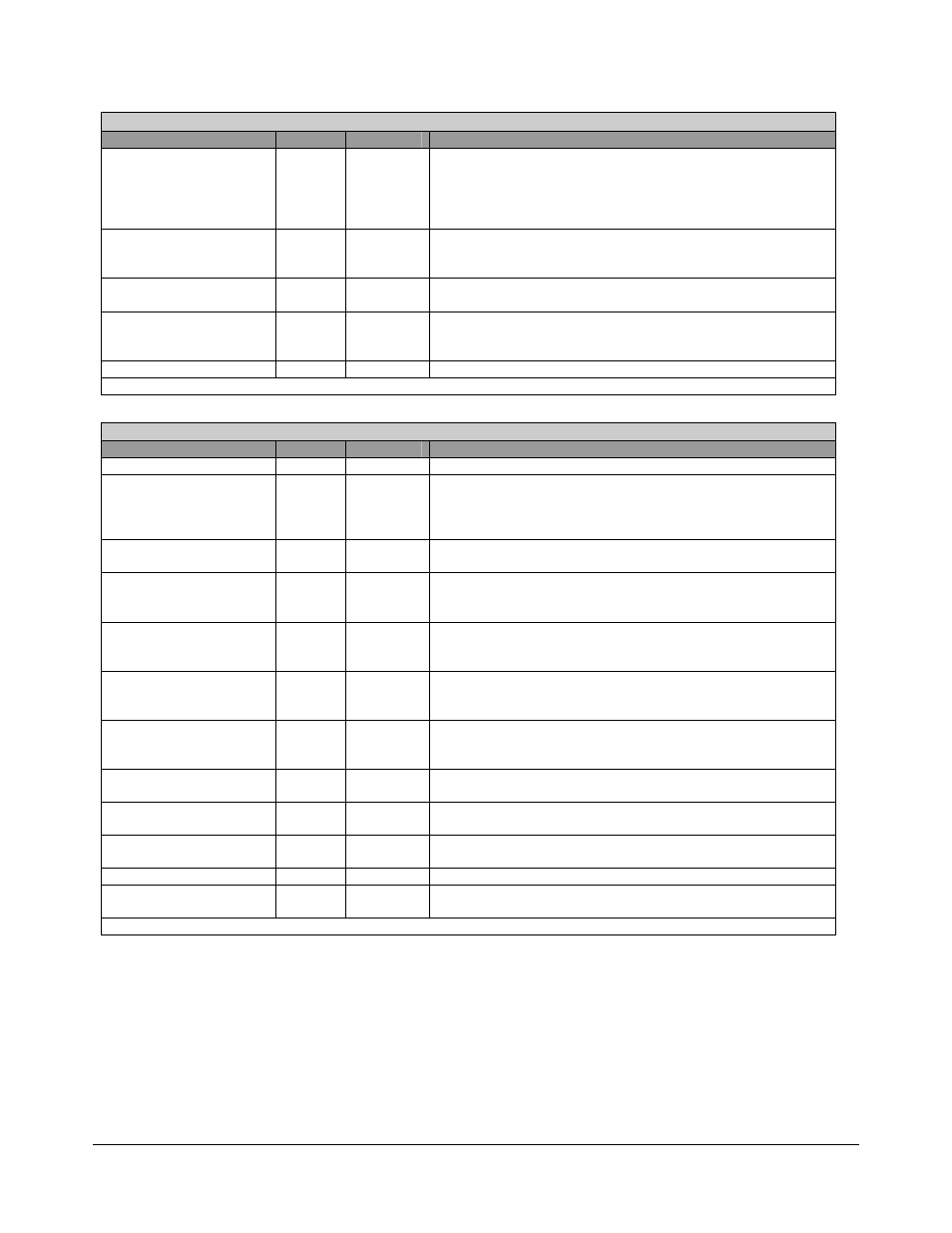

Command- RW - 16 bits - [PCI_Reg: 04h]

Field Name

Bits

Default

Description

Parity Error Response

6

0b

This bit controls the device’s response to parity errors. When

the bit is set, the device must take its normal action when a

parity error is detected. When the bit is 0, the device must

ignore any parity errors that it detects and continue normal

operation.

Wait Cycle Control

7

0b

This bit is used to control whether or not a device does

address/data stepping. This module does not use address

stepping. [Read-only]

SERR# Enable

8

0b

This bit is an enable bit for SERR# driver. A value of 0

disables the SERR# and a value of 1 enables it.

Fast Back-to-Back

Enable

9

0b

This bit indicates whether device is fast back-to-back capable.

ACPI/SMbus does not support this function and so this bit is

always 0. [Read-only]

Reserved 15:10

00h

PCI Command register

STATUS- RW - 16 bits - [PCI_Reg: 06h]

Field Name

Bits

Default

Description

Reserved 3:0

MSI Mapping Capability

4

1/0b

[Read-only] This bit indicates whether the device can support

MSI mapping. For K8 system this device is MSI mapping

capable so default value is 1; for P4 system this device does

not support MSI mapping so default value is 0.

66 MHz Capable

5

1b

This bit indicates whether the device can support 66 MHz.

This device is 66 MHz capable. [Read-only]

UDF Supported

6

0b

This bit indicates whether the device supports user definable

feature. This module does not support this feature and so it is

always 0. [Read-only]

Fast Back-to-Back

Capable

7

0b

This bit indicates whether the device is capable of fast back-to-

back cycles. This module does not support this feature and so

it is always 0. [Read-only]

Data Parity Error

Detected

8

0b

Set to 1 if the Parity Error Response bit is set, and the module

has detected PERR# asserted while acting as a PCI master

(regardless PERR# was driven by this module).

DEVSEL Timing

10:9

01b

These bits encode the timing of DEVSEL#. This module will

always respond in medium timing and so these bits are always

11.

Signaled Target Abort

11

0b

This bit is set by a slave device whenever it terminates a cycle

with a Target-Abort.

Received Target Abort

12

0b

This bit is set by a master device whenever its transaction is

terminated with a Target-Abort.

Received Master Abort

13

0b

This bit is set by a slave device whenever it terminates its

transaction with Master-Abort.

Signaled System Error

14

0b

This bit is set by device whenever the device asserts SERR#.

Detected Parity Error

15

0b

This bit is set by device whenever it detects a parity error,

even if parity error handling is disabled.

PCI device status register