AMD SB600 User Manual

Page 160

©2008 Advanced Micro Devices, Inc.

SMBus Module and ACPI Block (Device 20, Function 0)

AMD SB600 Register Reference Manual

Proprietary

Page 160

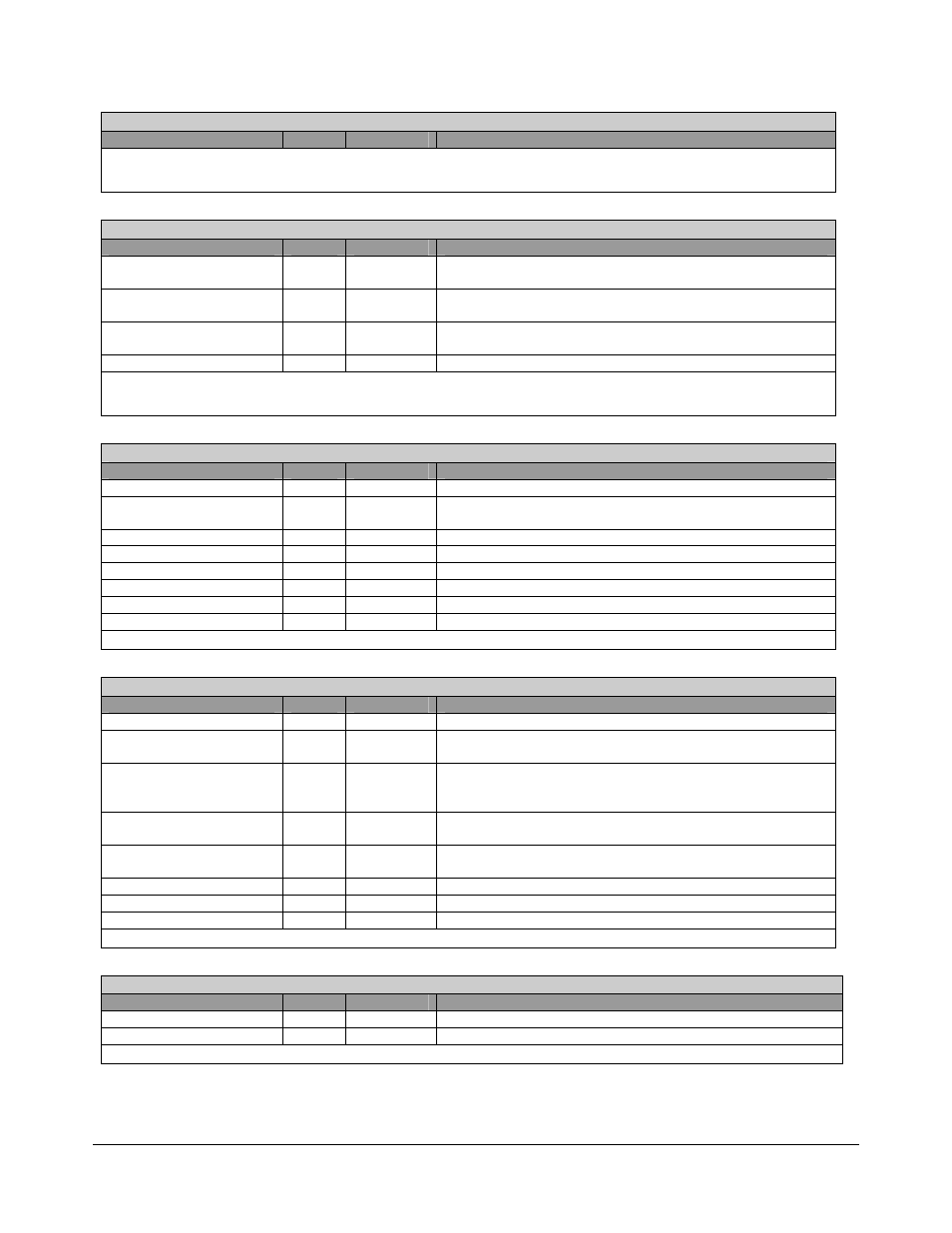

MwaitEnable - RW – 8 bits - [PM_Reg: 5Eh]

Field Name

Bits

Default

Description

MwaitEnable register

This register is used only in the P4 system.

MwaitSmiSts - RW – 8 bits - [PM_Reg: 5Fh]

Field Name

Bits

Default

Description

Mwait_any_smi_sts

0

0b

This bit indicates that SMI# is generated when any CPU is in

mwait state

Mwait_2cpu_smi_sts

1

0b

This bit indicates that for 2 CPU system (dual core, non HT)

SMI# is generated when both CPUs are in mwait state

Mwait_4cpu_smi_sts

2

0b

This bit indicates that for 4 CPU system (dual core, HT) SMI#

is generated when all 4 CPUs are in mwait state

Reserved 7:3

00h

MwaitSmiSts register

This register is used only in the P4 system.

Options_0 - RW – 8 bits - [PM_Reg: 60h]

Field Name

Bits

Default

Description

TAlertFanEn

0

0b

Set this bit to put all fans to full speed if TALERT# is asserted

ProcHotFanEn

1

0b

Set this bit to put all fans to full speed if PROCHOT# is

asserted

Fan1En

2

0b

Setting this bit will configure GPIO48 pin to be FAN1 output

Fan2En

3

0b

Setting this bit will configure GPIO49 pin to be FAN2 output

Reserved 4

0b

SpkrEn

5

0b

Setting this bit will configure GPIO2 to be speaker output

Fan0En

6

0b

Setting this bit will configure GPIO3 to be FAN0 output

Reserved 7

0b

Options_0 register

Options_1 - RW – 8 bits - [PM_Reg: 61h]

Field Name

Bits

Default

Description

Reserved 0

0b

IsAmd

1

0b

Set to enable NB/SB handshake during IOAPIC interrupt for

AMD K6 or K7 class; Clear for other CPU.

PCI_Active_enable

2

0b

BIOS should set this bit in order to monitor BM_STS pin from

NB (the pin is called BMREQ# on SB) and bus mastering

from the SB itself.

UseCpuRst

3

1b

If this bit is not set, then system reset will cause INIT# instead

of CPURST#.

ProcHotStsEn

4

0b

Set to enable PROCHOT# to generate TwarnStatus and

thermal throttle

Reserved 5

0b

UsbPmeEnable

6

0b

USB PME enable

Reserved 7

0b

Options_1 register

Shadow_SCI- R – 8 bits - [PM_Reg: 62h]

Field Name

Bits

Default

Description

Shadow_SCI 0

0b

SCI

output

Reserved 7:1

00h

Shadow_SCI register