AMD SB600 User Manual

Page 90

©2008 Advanced Micro Devices, Inc.

OCHI USB 1.1 and EHCI USB 2.0 Controllers

AMD SB600 Register Reference Manual

Proprietary

Page 90

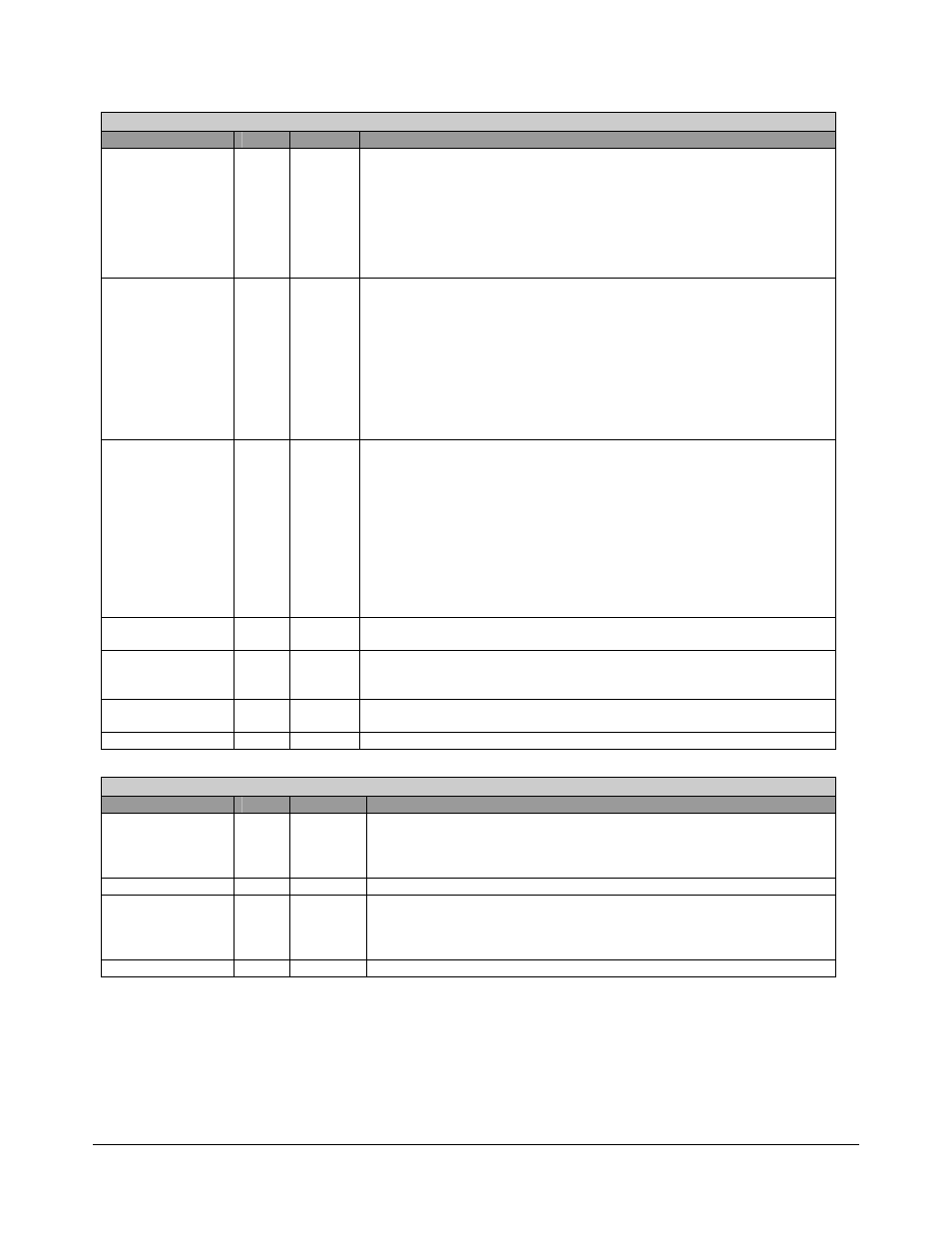

PORTSC (1-N_PORTS) –RW - 32 bits - [EOR_Reg : EHCI_EOR + (44h~68h)]

Field Name

Bits

Default

Description

Port Owner

13

1b

This bit unconditionally goes to a 0b when the Configured bit in the

CONFIGFLAG register makes a 0b to 1b transition. This bit

unconditionally goes to 1b whenever the Configured bit is zero.

System software uses this field to release ownership of the port to a

selected host controller (in the event that the attached device is not a

high-speed device). Software writes a one to this bit when the attached

device is not a high-speed device. A one in this bit means that a

companion host controller owns and controls the port.

Port Indicator

Control

15:14

00b

Writing to this bit has no effect if the P_INDICATOR bit in the

HCSPARAMS register is a zero. If P_INDICATOR bit is a one, then the bit

encodings are:

Bit Value Meaning

00b Port indicators are off

01b Amber

10b Green

11b Undefined

Refer to the USB Specification Revision 2.0 for a description on how

these bits are to be used. This field is zero if Port Power is zero.

Port Test Control

19:16

0000b

When this field is zero, the port is NOT operating in a test mode. A non-

zero value indicates that it is operating in test mode and the specific test

mode is indicated by the specific value. The encoding of the test mode

bits are (0110b - 1111b are reserved):

Bits Test Mode

0000b Test mode not enabled

0001b Test J_STATE

0010b Test K_STATE

0011b Test SE0_NAK

0100b Test Packet

0101b Test FORCE_ENABLE

Wake on Connect

Enable

20

0b

Writing this bit to a one enables the port to be sensitive to device

connects as wake-up events. This field is zero if Port Power is zero.

Wake on

Disconnect

Enable

21

0b

Writing this bit to a one enables the port to be sensitive to device

disconnects as wake-up events. This field is zero if Port Power is zero.

Wake on Over-

current Enable

22

0b

Writing this bit to a one enables the port to be sensitive to over-current

conditions as wake-up events. This field is zero if Port Power is zero.

Reserved 31:23

Reserved

Packet Buffer Threshold Values – RW - 32 bits - [EOR_Reg : EHCI_EOR + 84h]

Field Name

Bits

Default

Description

IN Threshold

7:0

10h

The PCI transaction starts when threshold of internal FIFO for receive

packet is reached.

The value represents multiple of 8 bytes – 10h means 128 bytes. The

smallest acceptable value is 08h (64 bytes).

Reserved 15:8

Reserved

OUT Threshold

23:16

60h

The transmit packet starts at UTMI interface when threshold of internal

FIFO for transmit packet is reached.

The value represents multiple of 8 bytes – 10h means 128 bytes. The

smallest acceptable value is 08h (64 bytes).

Reserved 31:24

Reserved