AMD SB600 User Manual

Page 152

©2008 Advanced Micro Devices, Inc.

SMBus Module and ACPI Block (Device 20, Function 0)

AMD SB600 Register Reference Manual

Proprietary

Page 152

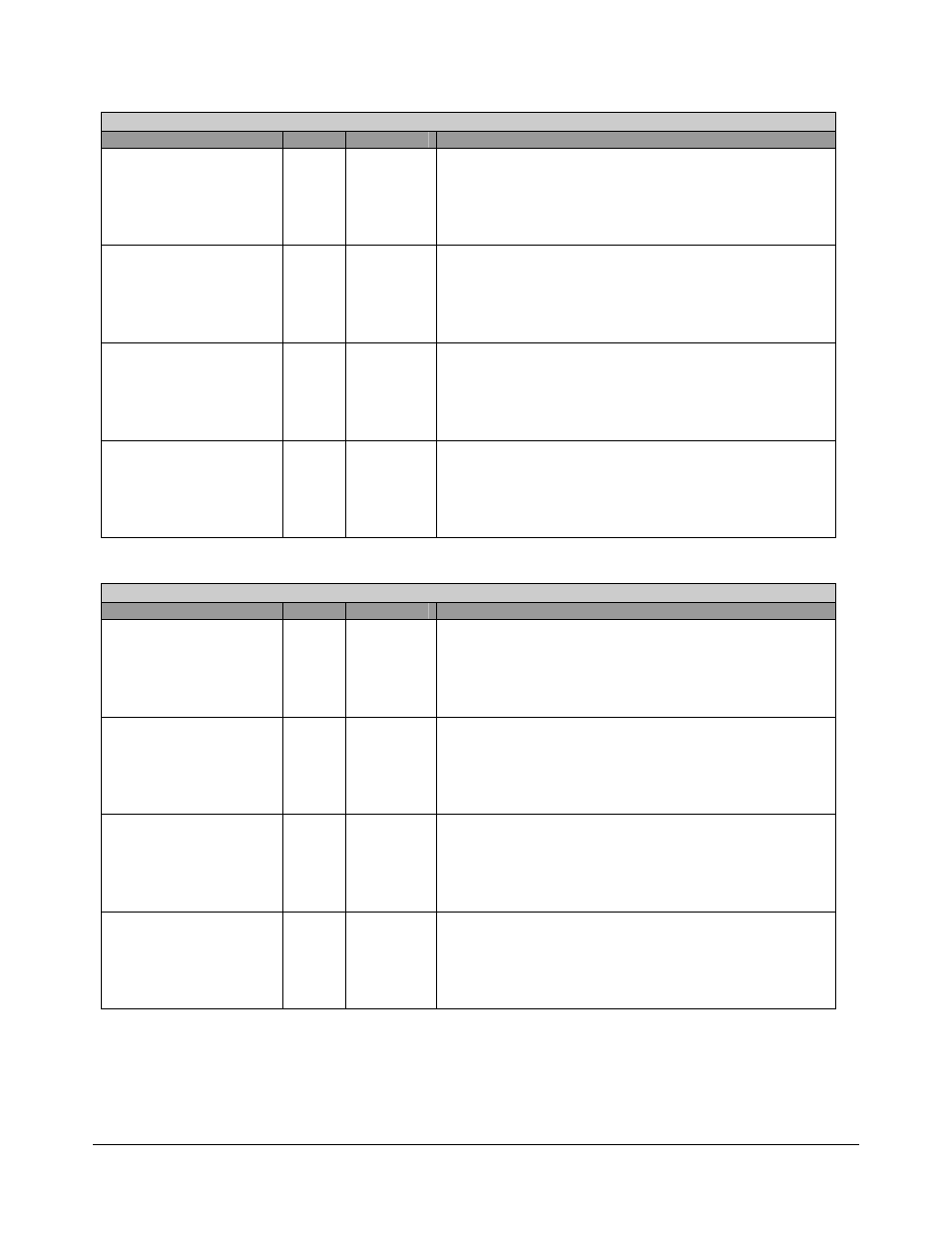

GPMConfig2- RW – 8 bits - [PM_Reg: 34h]

Field Name

Bits

Default

Description

Gpio0Config

1:0

00b

These two bits configure Gpio0 or WAKE#

00 ACPI Event (trigger SCIOUT or SMI#

depending on SCI_EN bit)

01 Gpio0 to generate SMI#

10 Gpio0 to generate SMI# followed by SCI

11 Gpio0 to generate IRQ13

Gpm4Config

3:2

00b

These two bits configure GPM4

00 ACPI Event (trigger SCIOUT or SMI#

depending on SCI_EN bit)

01 Gpm4 to generate SMI#

10 Gpm4 to generate SMI# followed by SCI

11 Gpm4 to generate IRQ13

Gpm5Config

5:4

00b

These two bits configure GPM5

00 ACPI Event (trigger SCIOUT or SMI#

depending on SCI_EN bit)

01 Gpm5 to generate SMI#

10 Gpm5 to generate SMI# followed by SCI

11 Gpm5 to generate IRQ13

AzPmeConfig

7:6

00b

These two bits configure AzPme

00 ACPI Event (trigger SCIOUT or SMI#

depending on SCI_EN bit)

01 AzPme to generate SMI#

10 AzPme to generate SMI# followed by SCI

11 AzPme to generate IRQ13

GPMConfig3 – RW – 8 bits - [PM_Reg: 35h]

Field Name

Bits

Default

Description

Gpm6Config

1:0

00b

These two bits configure GPM6

00 ACPI Event (trigger SCIOUT or SMI#

depending on SCI_EN bit)

01 Gpm6 to generate SMI#

10 Gpm6 to generate SMI# followed by SCI

11 Gpm6 to generate IRQ13

Gpm7Config

3:2

00b

These two bits configure GPM7

00 ACPI Event (trigger SCIOUT or SMI#

depending on SCI_EN bit)

01 Gpm7 to generate SMI#

10 Gpm7 to generate SMI# followed by SCI

11 Gpm7 to generate IRQ13

Gpio2Config

5:4

00b

These two bits configure Gpio2

00 ACPI Event (trigger SCIOUT or SMI#

depending on SCI_EN bit)

01 Gpio2 to generate SMI#

10 Gpio2 to generate SMI# followed by SCI

11 Gpio2 to generate IRQ13

SataSciConfig

7:6

00b

These two bits configure SataSci

00 ACPI Event (trigger SCIOUT or SMI#

depending on SCI_EN bit)

01 SataSci to generate SMI#

10 SataSci to generate SMI# followed by SCI

11 SataSci to generate IRQ13