AMD SB600 User Manual

Page 183

©2008 Advanced Micro Devices, Inc.

SMBus Module and ACPI Block (Device 20, Function 0)

AMD SB600 Register Reference Manual

Proprietary

Page 183

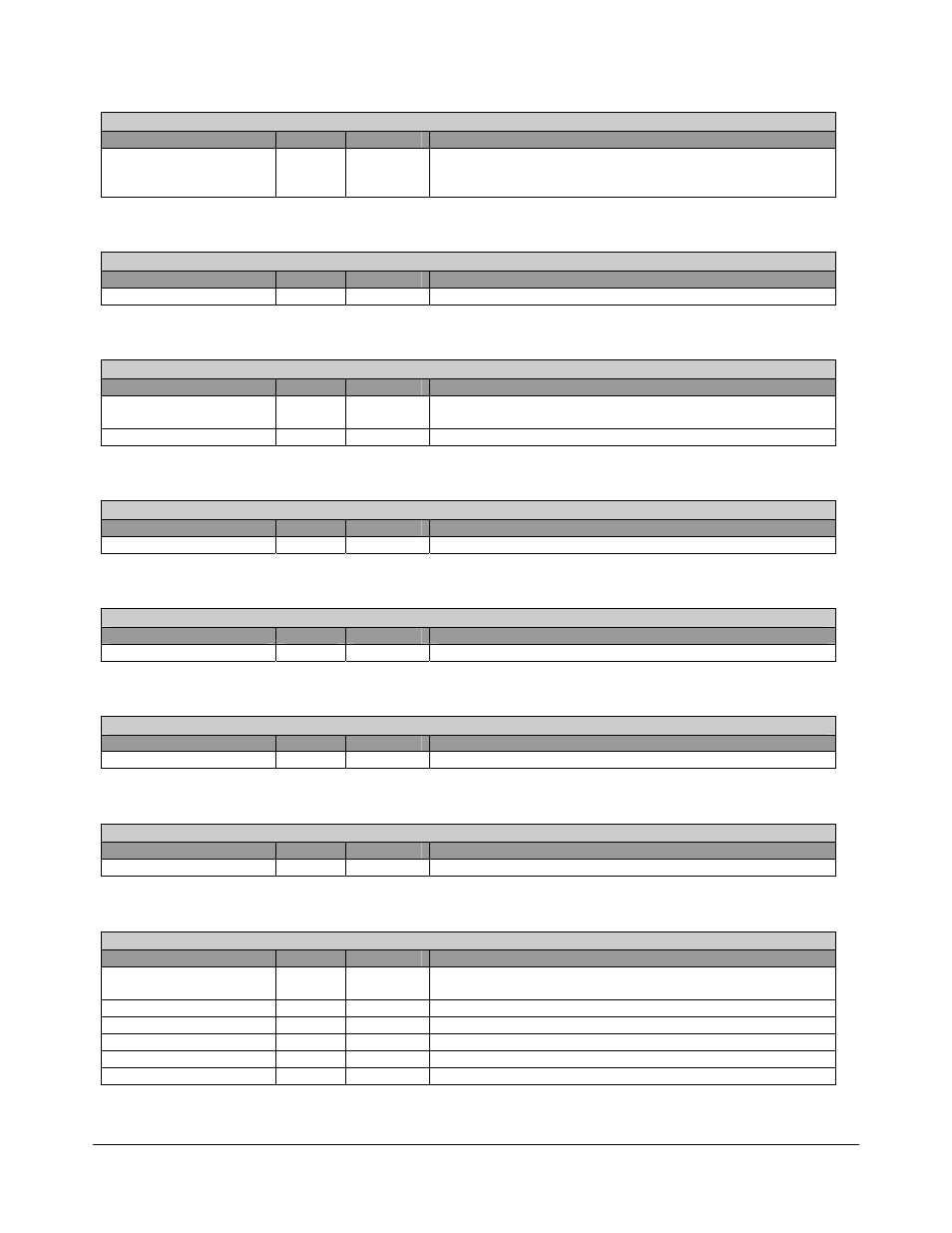

HostControl – RW - 8 bits - [ASF_IO: 02h]

Field Name

Bits

Default

Description

PECEnable

7

0b

0: PEC disable

1: PEC enable, enable CRC checking when ASF HC presents

as SM master and SM slave.

HostCommand – RW - 8 bits - [ASF_IO: 03h]

Field Name

Bits

Default

Description

HostCommand

7:0

00h

Command to be transmitted by master

SlaveAddress– RW - 8 bits - [ASF_IO: 04h]

Field Name

Bits

Default

Description

RW 0

0b

0:

Write

1: Read

Address 7:1

00h

Provide

the SM address of Slave

Data0– RW - 8 bits - [ASF_IO: 05h]

Field Name

Bits

Default

Description

Data0

7:0

00h

Contains count or DATA0 field of transaction

Data1– RW - 8 bits - [ASF_IO: 06h]

Field Name

Bits

Default

Description

Data1 7:0

00h

Contains

DATA1 field of transaction

DataIndex– RW - 8 bits - [ASF_IO: 07h]

Field Name

Bits

Default

Description

DataIndex

7:0

00h

Index to 32 Data registers.

PEC– RW - 8 bits - [ASF_IO: 08h]

Field Name

Bits

Default

Description

PEC

7:0

00h

PEC byte to be sent to slave.

ASFStatus– RW - 8 bits - [ASF_IO: 0Ah]

Field Name

Bits

Default

Description

EnableStatus

7

0b

1: Reset all the status bit in this register.

0: Enable status bit in this register

Reserved 6:4

000b

RemotePowerCycle

3

0b

Power cycle has happened from ASF

RemotePowerUp

2

0b

Power up has happened. from ASF

RemotePowerDown

1

0b

Power down has happened from ASF

RemoteReset

0

0b

Reset has happened from ASF