AMD SB600 User Manual

Page 223

©2008 Advanced Micro Devices, Inc.

AC ’97 Controller Functional Descriptions

AMD SB600 Register Reference Manual

Proprietary

Page 223

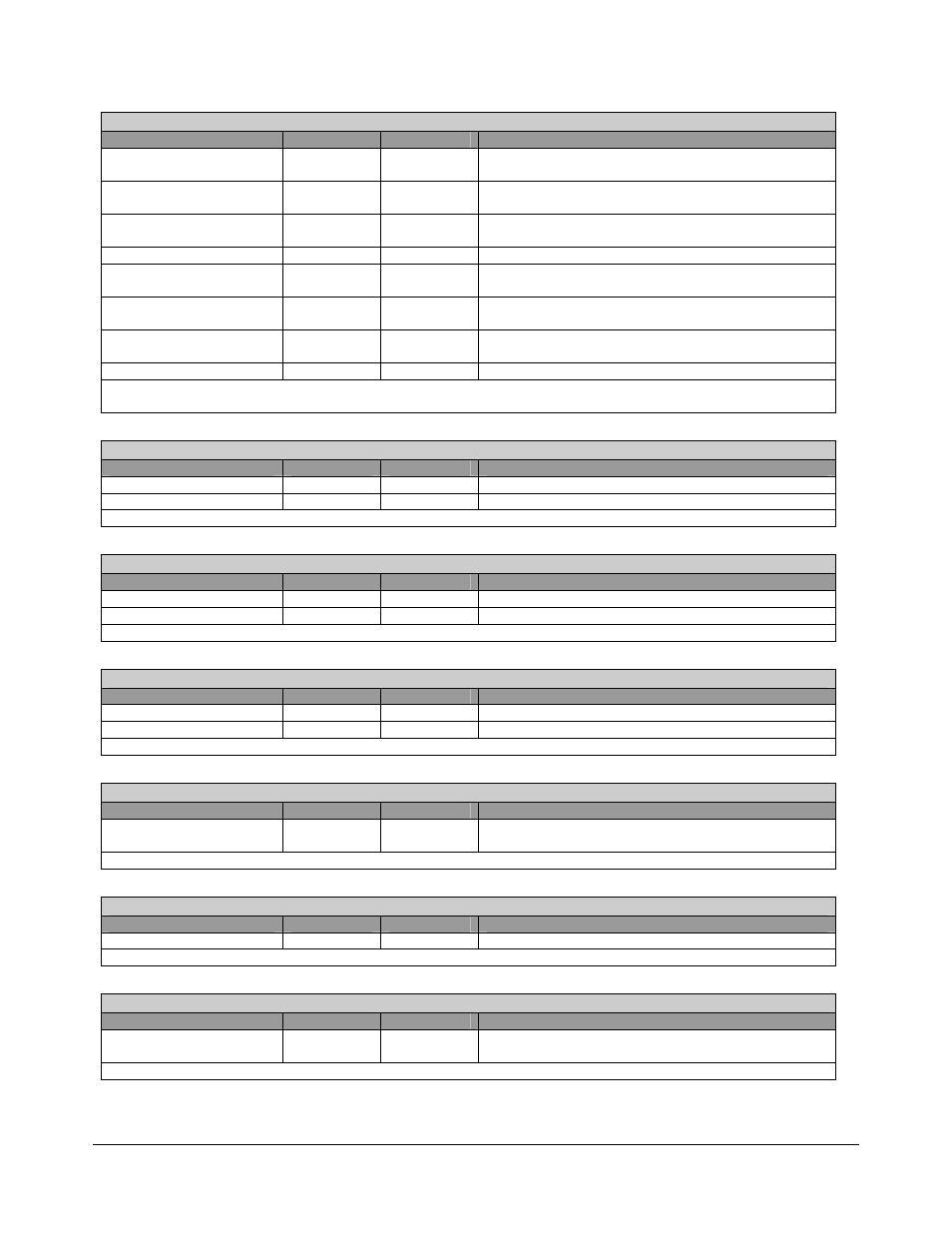

Output DMA 1/2/3 Threshold – RW - 32 bits - [MEM_Reg: 34h]

Field Name

Bits

Default

Description

out DMA #1 State

2:0

0h

Current state of out DMA # 1 (Modem 1 for slot 5)

[Read-only]

out DMA #2 State

5:3

0h

Current state of out DMA # 2 (Modem 2 for slot 10)

[Read-only]

out DMA #3 State

8:6

0h

Current state of out DMA # 3 (Handset for slot 11)

[Read-only]

Reserved 15:9

00h

Output Threshold 1

20:16

00h

Threshold value for the Out DMA 1 FIFO. (FIFO size

4x20)

Output Threshold 2

25:21

00h

Threshold value for the Out DMA 2 FIFO. (FIFO size

4x20)

Output Threshold 3

30:26

00h

Threshold value for the Out DMA 3 FIFO. (FIFO size

4x20)

Reserved 31

0b

Output DMA1/2/3 Threshold Register: Configure Slot responsibility for Output channels 0 and also threshold values

of all out DMA FIFO's.

Output DMA1 Link List Pointer – RW - 32 bits - [MEM_Reg: 38h]

Field Name

Bits

Default

Description

out DMA1 LL ptr en.

0

0b

Output DMA1 Link List Pointer enable

out DMA1 LL ptr

31:1

0000_0000h Pointer to the start of the Link List - to the first DT.

Output DMA1 Link List Pointer Register:

Output DMA2 Link List Pointer – RW - 32 bits - [MEM_Reg: 3Ch]

Field Name

Bits

Default

Description

out DMA2 LL ptr en.

0

0b

Output DMA2 Link List Pointer enable

out DMA2 LL ptr

31:1

0000_0000h Pointer to the start of the Link List - to the first DT.

Output DMA2 Link List Pointer Register:

Output DMA3 Link List Pointer – RW - 32 bits - [MEM_Reg: 40h]

Field Name

Bits

Default

Description

out DMA3 LL ptr en.

0

0b

Output DMA3 Link List Pointer enable

out DMA3 LL ptr

31:1

0000_0000h Pointer to the start of the Link List - to the first DT.

Output DMA3 Link List Pointer Register:

Output DMA1 DT Start – R - 32 bits - [MEM_Reg: 44h]

Field Name

Bits

Default

Description

out DMA1 DT start

31:0

0000_0000h Pointer to the start of data associated with current DT

for the Output DMA1.

Output DMA1 Discrete Table (DT) Start Pointer Register:

Output DMA1 DT Next– R - 32 bits - [MEM_Reg: 48h]

Field Name

Bits

Default

Description

out DMA1 DT next

31:0

0000_0000h Pointer to the next DT for the Output DMA1

Output DMA1 DT Next Pointer Register:

Output DMA1 DT Current– R - 32 bits - [MEM_Reg: 4Ch]

Field Name

Bits

Default

Description

out DMA1 DT current

31:0

0000_0000h Pointer to the currently accessing memory address for

the Output DMA1.

Output DMA1 DT Current Pointer Register: