Asf sm bus host interface registers – AMD SB600 User Manual

Page 182

©2008 Advanced Micro Devices, Inc.

SMBus Module and ACPI Block (Device 20, Function 0)

AMD SB600 Register Reference Manual

Proprietary

Page 182

2.3.5

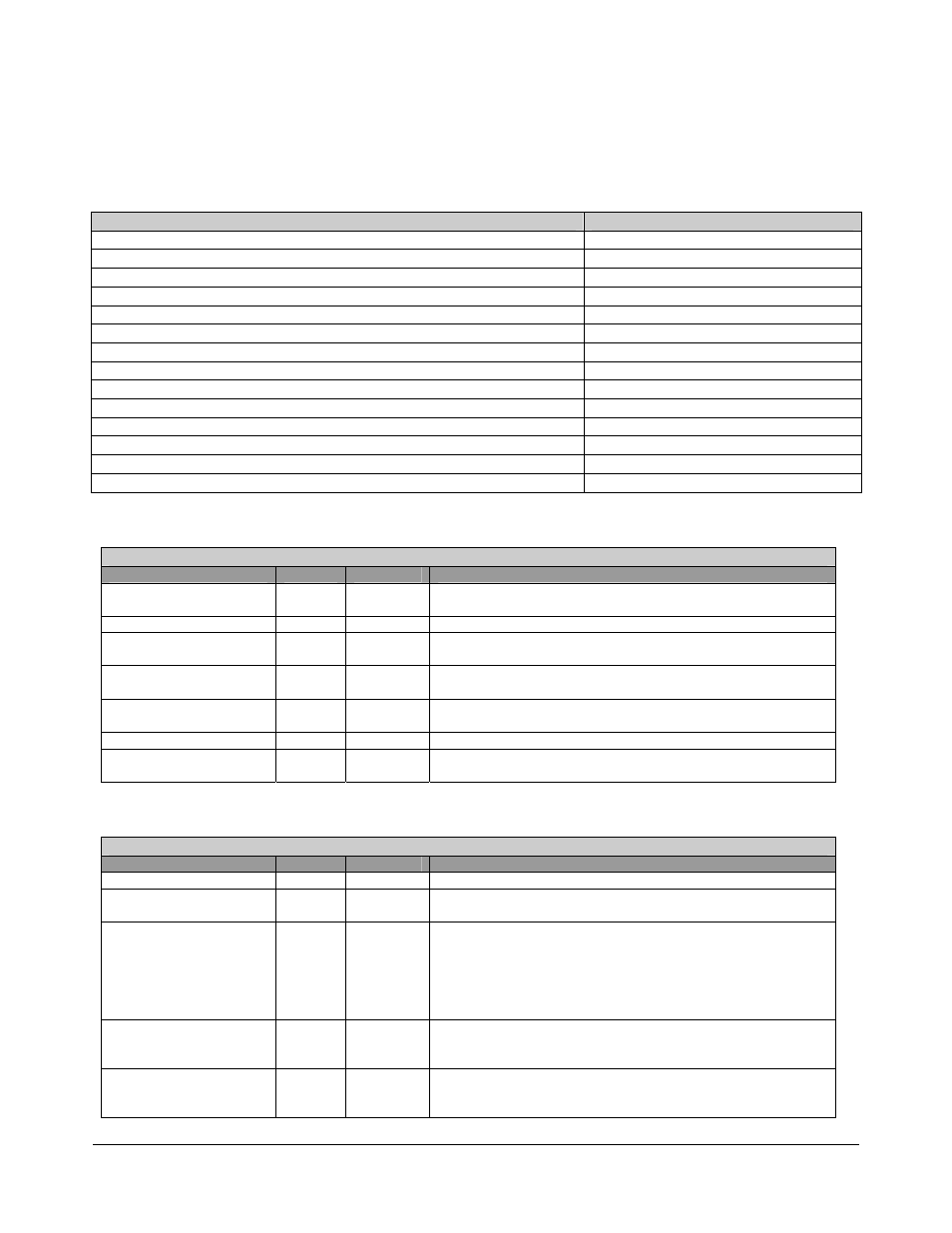

ASF SM bus Host Interface Registers

The ASF SM bus host register block is resident in the Io space whose base defined at offset 58h/59h of

config space.

Register Name

Offset Address

HostStatus 00h

HostControl 02h

HostCommand 03h

SlaveAddress 04h

Data0 05h

Data1 06h

Data 07h

PEC 08h

ASFStatus 0Ah

StatusMask0 0Bh

StatusMask1 0Ch

SlaveControl 0Dh

RemoteCtrlAdr 0Eh

SensorAdr 0Fh

HostStatus – R - 8 bits - [ASF_IO: 00h]

Field Name

Bits

Default

Description

HostBusy

0

0b

0 – SM bus Host is idle

1 – SM bus Host is busy

Reserve 1

0b

DevError

2

0b

0: Slave device behave correctly

1: No ACK or Slave device responses incorrectly

BusCollision

3

0b

0: No bus collision

1: Bus collision

PECError

4

0b

0: No CRC error

1: CRC error happens

Reserve 6:5

00b

LastByte

7

0b

0: Last byte has not received

1: Last byte has received

HostControl – RW - 8 bits - [ASF_IO: 02h]

Field Name

Bits

Default

Description

Reserved 0

0b

KillHost

1

0b

0 – Enable SM master

1 – Reset SM master

Protocol

4:2

000b

000: Quick

001: Byte

010: Byte Data

011: Word Data

100: Process call

101: Block

PECAppend

5

0b

0: No PEC append

1: Automatic PEC append. ASF HC calculates CRC code and

append to the tail of the data packets.

Start 6

0b

WO:

0: Always read 0 on reads

1: Writing 1 to initiate the command