AMD SB600 User Manual

Page 166

©2008 Advanced Micro Devices, Inc.

SMBus Module and ACPI Block (Device 20, Function 0)

AMD SB600 Register Reference Manual

Proprietary

Page 166

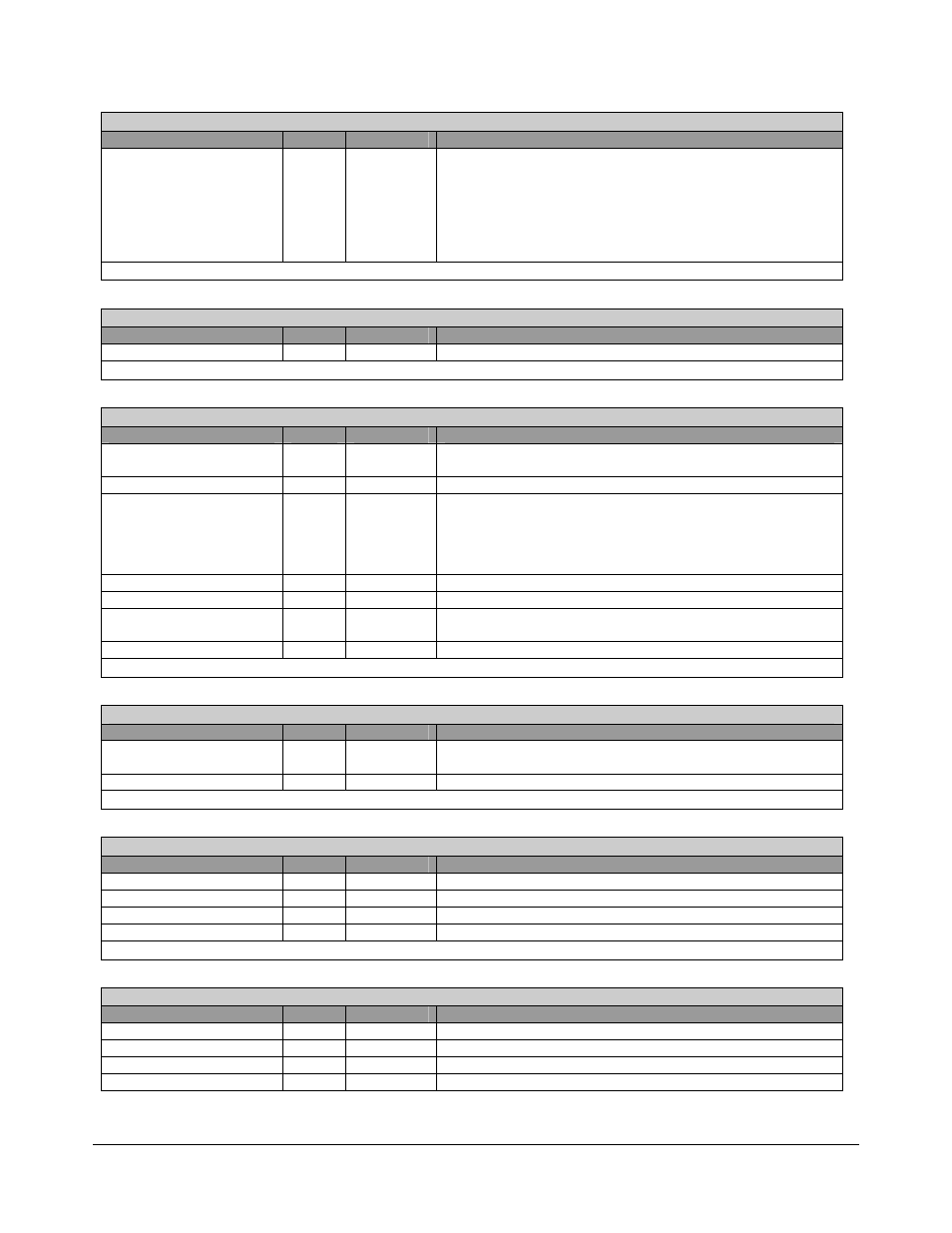

NoStatusControl0 – RW – 8 bits – [PM_Reg:7Ah]

Field Name

Bits

Default

Description

NoStatusControl0 7:0

00h

For

GEVENT#[7:0]

configured as PME# (wakeup function),

additional setting of these bits will still allow GEVENT# pins to

wakeup the system but they will not set the status bit in the

ACPI GEVENT status register.

Bits [7:0] control GEVENT#[7:0] respectively

0 – Allow status

1 – Not-allow status

NoStatusControl0 register

NoStatusControl1 – RW – 8 bits – [PM_Reg:7Bh]

Field Name

Bits

Default

Description

NoStatusControl1 7:0

00h

This register should be set the same as 7A

NoStatusControl1 register

MiscEnable7C – RW – 8 bits – [PM_Reg:7Ch]

Field Name

Bits

Default

Description

BreakEnable

0

0b

Set to 1 to allow wakeup from C3 without asserting LDTSTP#

in K8 system

Reserved 1

0b

BlinkControl

3:2

00b

Blinking interval select

00: Always off

01: 1sec on, 3sec off, repeating

10: 2sec on, 2sec off, repeating

11: Always on

AltCenturyEnable

4

0b

Set to 1 to enable RTC AltCentury register

SusStatOption

5

0b

SUS_STAT# timing option enable

WaitStpGntEnB

6

0b

0: Wait for STPGNT# in ACPI S state;

1: No wait

Reserved 7

0b

MiscEnable7C register

DprSlpVrMinTime – RW – 8 bits – [PM_Reg:7Dh]

Field Name

Bits

Default

Description

DprSlpVrMinTime

3:0

2h

This defines the minimum assertion time of DPRSLPVR, in

2us increment with 2us uncertainty.

Reserved 7:4

0h

DprSlpVrMinTime register

SMAF0 – RW – 8 bits – [PM_Reg:80h]

Field Name

Bits

Default

Description

S45SMAF

2:0

110b

System management action field for S4/5 STPCLK message

Reserved 3

0b

C2SMAF

6:4

0h

System management action field for C2 STPCLK message

Reserved 7

0b

SMAF0 register

SMAF1 – RW – 8 bits – [PM_Reg:81h]

Field Name

Bits

Default

Description

C3SMAF

2:0

001b

System management action field for C3 STPCLK message

Reserved 3

0b

VFSMAF

6:4

010b

System management action field for VFID STPCLK message

Reserved 7

0b