AMD SB600 User Manual

Page 268

©2008 Advanced Micro Devices, Inc.

Host PCI Bridge Registers (Device 20, Function 4)

AMD SB600 Register Reference Manual

Proprietary

Page 268

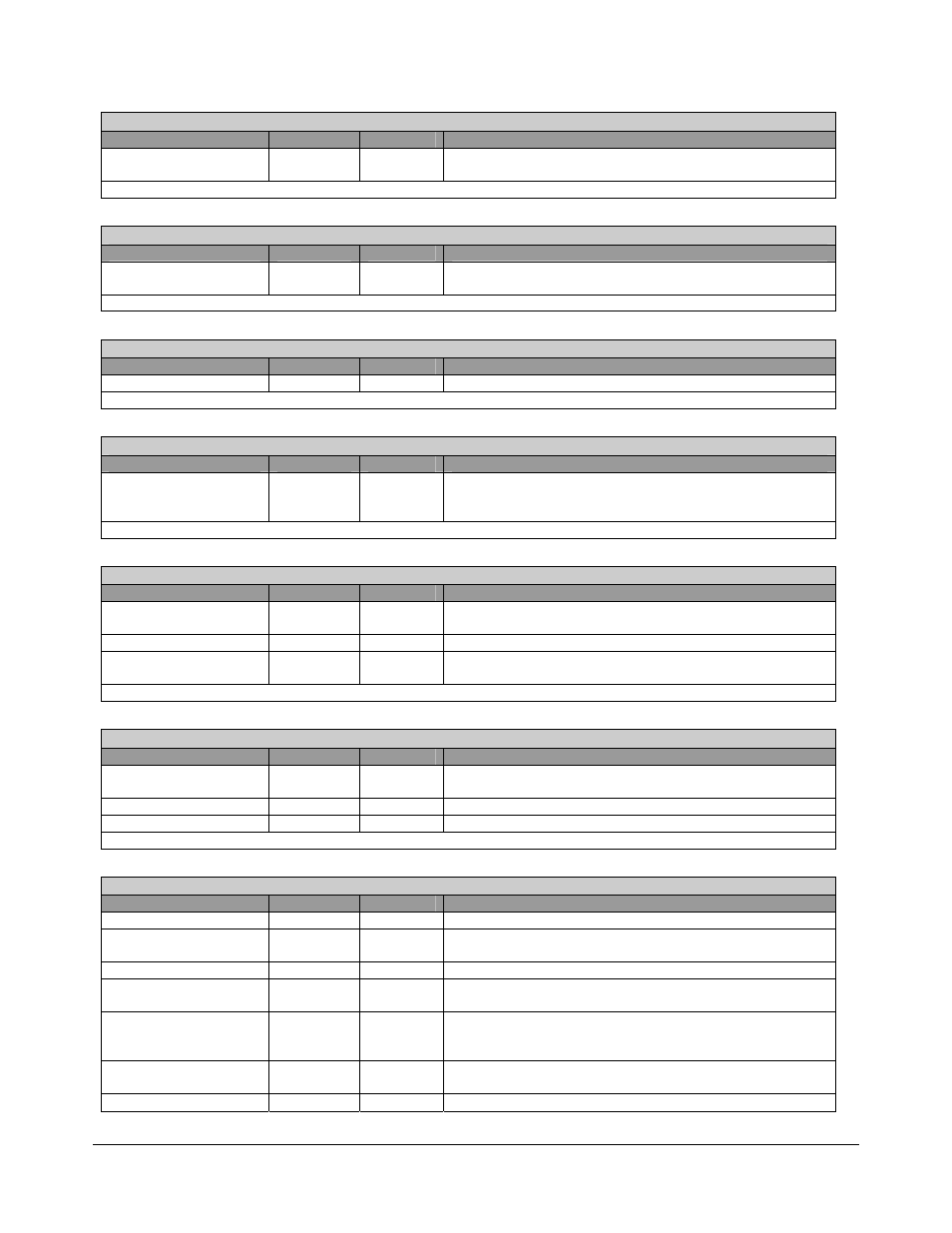

Primary Bus Number- RW - 8 bits - [PCI_Reg: 18h]

Field Name

Bits

Default

Description

Primary Bus Number

7:0

00h

Bus number of the PCI bus to which the primary interface is

connected.

Primary Bus Number register

Secondary Bus Number - RW - 8 bits - [PCI_Reg: 19h]

Field Name

Bits

Default

Description

Secondary Bus Number

7:0

00h

Bus number of the PCI bus to which the secondary interface

is connected.

Secondary Bus Number register

SUBBN- RW - 8 bits - [PCI_Reg: 1Ah]

Field Name

Bits

Default

Description

SubordinateBusNum

7:0

00h

Bus number of the highest numbered PCI bus behind PCIB.

Subordinate Bus Number register

Secondary Latency Timber- RW - 8 bits - [PCI_Reg: 1Bh]

Field Name

Bits

Default

Description

Secondary Latency

Timer

7:0

00h

Secondary Master latency control timer. Sets the minimum

time that the Secondary bus master can retain the

ownership of the bus.

Secondary Master Latency Timer register

IO Base- RW - 8 bits - [PCI_Reg: 1Ch]

Field Name

Bits

Default

Description

IO16

1:0

00b

Indicates a 16-bit IO address space. Read Only

Can be changed to 32-bit when bit[29] of regx48 is set

Reserved 3:2

00b

Reserved

IOBase

7:4

0h

Defines the bits [15:12] of the base address of 16-bit or 32-

bit IO space.

IO base register

IO Limit- RW - 16 bits - [PCI_Reg: 1Dh]

Field Name

Bits

Default

Description

IO16

1:0

00b

Indicates a 16-bit IO address space. Read Only

Can be changed to 32-bit when bit[29] of regx48 is set

Reserved 3:2

00b

Reserved

IO Limit

7:4

0h

Defines bits [15:12] of the limit of 16-bit or 32-bit IO space.

IO Limit register

Secondary Status- RW - 16 bits - [PCI_Reg: 1Eh]

Field Name

Bits

Default

Description

Reserved 4:0

00h

Reserved

Sec 66MHz Capable

5

0b

Indicates PCIB doesn’t support 66MHz secondary interface.

Read Only.

Reserved 6

0b

Reserved

Secondary Fast Back-

to-Back Capable

7

1b

Indicates PCIB is capable of accepting fast back-to-back

transactions on the secondary bus. Read Only.

Secondary Master Data

Parity Error

8

0b

Master Data Parity Error on the secondary bus, assertion of

S_PERR# (when PCIB acts as a master) is received, write

clears it.

Secondary DevSel

Timing

10:9

01b

DEVSEL# timing, indicates PCIB will assert DEVSEL# with

medium timing on the secondary bus. Read Only.

Secondary Target Abort

11

0b

Signaled Target Abort on the secondary bus, write clears it.