AMD SB600 User Manual

Page 117

©2008 Advanced Micro Devices, Inc.

SMBus Module and ACPI Block (Device 20, Function 0)

AMD SB600 Register Reference Manual

Proprietary

Page 117

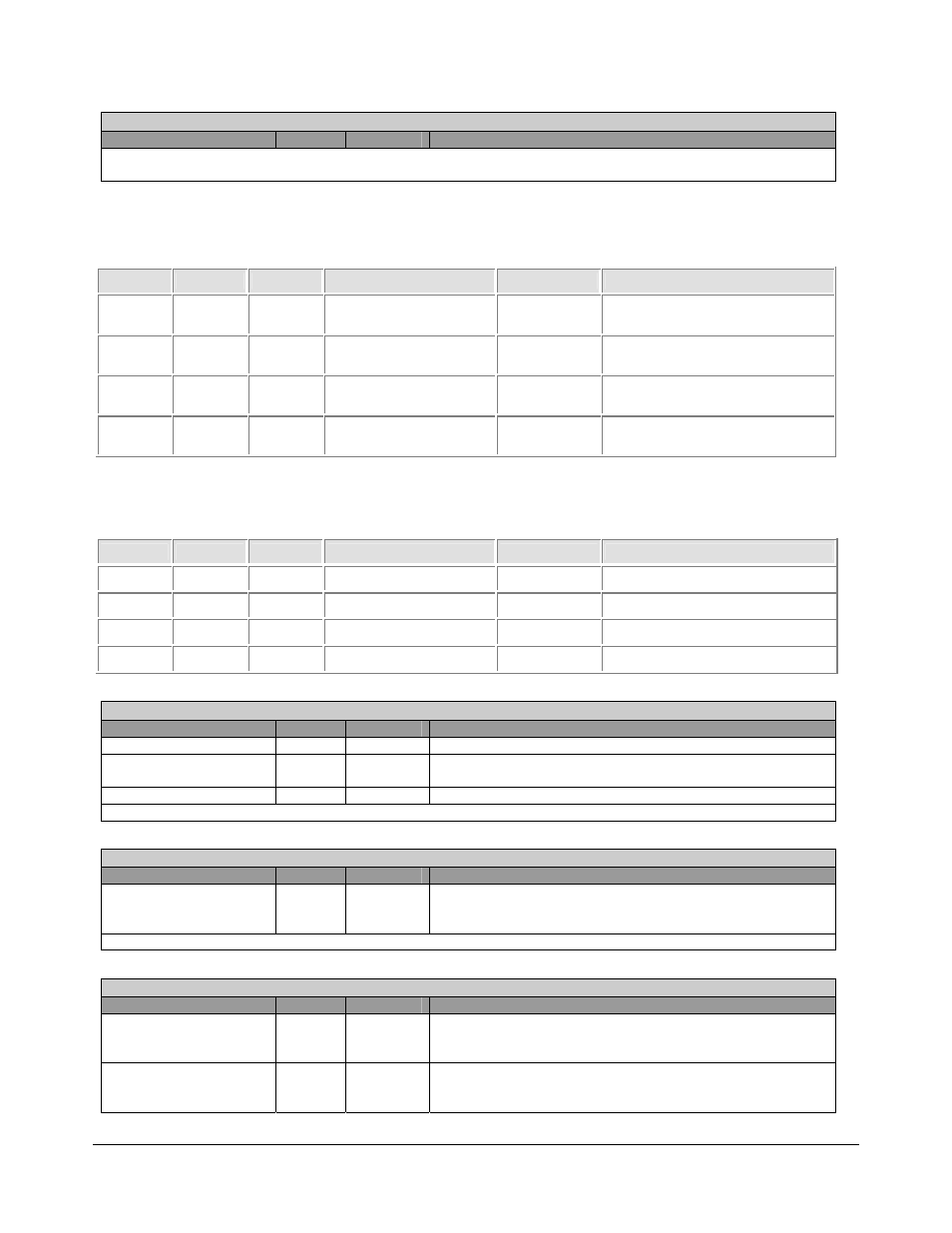

IoDrvSth - RW - 32 bits - [PCI_Reg: C0h]

Field Name

Bits

Default

Description

For control with only two bits, one can assume the four drive strength settings (corresponding to 25, 50, 75, and

100% respectively).

For the PCI interface, bits [3:0] and 26 control the AD and PCI control signals, The table below contains

recommendations based on empirical data collected from a live system:

S2

S1

S0

Percent Drive Strength

Loads

SMBUS PCI Register, Index C0h

0

0

0

33%

For 0-1 loads

Bits[1:0] = 01; Bits[3:2] = 00, bit 26

= 0

0

0

1

44%

For 2 loads

Bits[1:0] = 10; Bits[3:2] = 00, bit 26

= 1

0

1

0

55%

For 3-4 loads

Bits[1:0] = 01; Bits[3:2] = 01, bit 26

= 0

0

1

1

66%

For 4-5 loads

Bits[1:0] = 01; Bits[3:2] = 01, bit 26

= 1

For LPC bus, the drive strength is determined by SMBUS PCI C0h, bits [11:10] and [28]

S2

S1

S0

Percent Drive Strength

Loads

SMBUS PCI Register, Index C0h

0

0

0

33%

For 0-1 loads

Bits[11:10] = 00, bit 28 = 0

0

0

1

44%

For 2 loads

Bits[11:10] = 00, bit 28 = 1

0

1

0

55%

For 3-4 loads

Bits[11:10] = 01, bit 28 = 0

0

1

1

66%

For 4-5 loads

Bits[11:10] = 01, bit 28 = 1

I2CbusConfig - RW - 8 bits - [PCI_Reg: D2h]

Field Name

Bits

Default

Description

I2CController Enable

0

0b

I2C controller host interface enable

I2CbusInterrupt

1

0b

0 : SMI#

1 : IRQ

Reserved 7:2

00h

I2CbusConfig register: Registers D2-D5 control the interface when this chip is the I2C slave.

I2CCommand - RW - 8 bits - [PCI_Reg: D3h]

Field Name

Bits

Default

Description

I2Ccommand

7:0

00h

I2C Host Slave Command; this value specifies the command

value to be matched for I2C master accesses to the

I2Ccontroller host slave interface.

I2CCommand register

I2CShadow1- RW - 8 bits - [PCI_Reg: D4h]

Field Name

Bits

Default

Description

Read/Write ShadowPort1

0

0b

Read/Write for Shadow Port 1

This bit must be programmed to 0 because I2C slave

controller only responds to Word Write Transaction.

I2CslaveAddr1

7:1

00h

SMBus Slave Address for shadow port 1

This value specifies the address used to match against

incoming I2C addresses for Shadow port 1.