AMD SB600 User Manual

Page 244

©2008 Advanced Micro Devices, Inc.

HD Audio Controllers Registers

AMD SB600 Register Reference Manual

Proprietary

Page 244

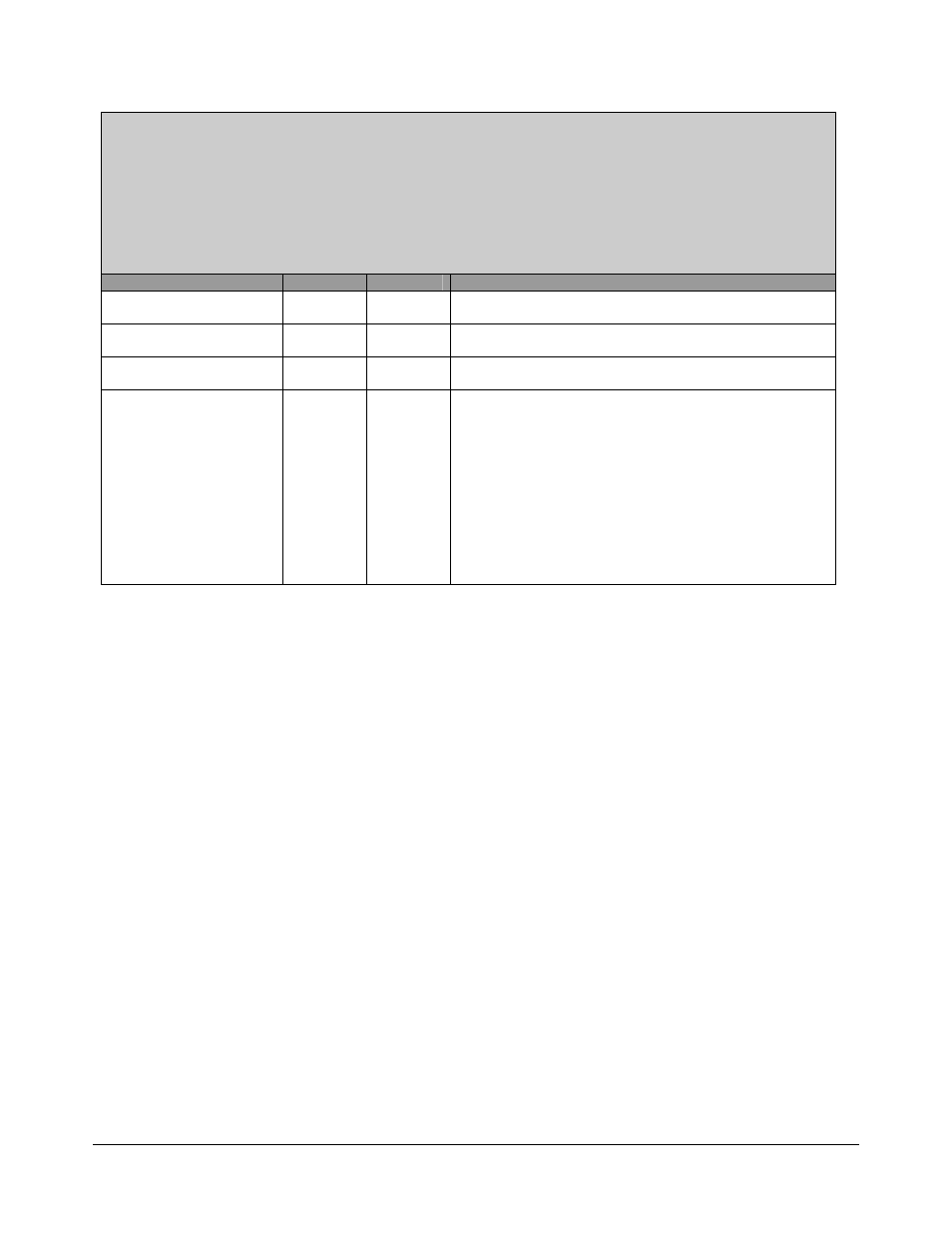

Stream Descriptor Control – RW – 24 bits

Input Stream 0 - [Mem_Reg: Base + 80h]

Input Stream 1 - [Mem_Reg: Base + A0h]

Input Stream 2 - [Mem_Reg: Base + C0h]

Input Stream 3 - [Mem_Reg: Base + E0h]

Output Stream 0 - [Mem_Reg: Base + 100h]

Output Stream 1 - [Mem_Reg: Base + 120h]

Output Stream 2 - [Mem_Reg: Base + 140h]

Output Stream 3 - [Mem_Reg: Base + 160h]

Field Name

Bits

Default

Description

Stripe Control

17:16

0h

The hardware only supports one SDO, this field has no

functional impact.

Traffic Priority

18

0b

If set to “1”, it will cause the controller to generate non-

snooped traffic.

Bidirectional Direction

Control

19

0b

The hardware does not support bi-direction, this field has

no impact.

Stream Number

23:20

0h

The value reflects the Tag associated with the data being

transferred on the link.

When data controlled by this descriptor is sent out over the

link, it will have this stream number encoded on the SYNC

signal.

When an input stream is detected on any of the SDIN_x

signals that match this value, the data are loaded into the

FIFO associated with this descriptor.

0000b = Reserved

0001b = Stream 1

:

1111b = Stream 15