AMD SB600 User Manual

Page 272

©2008 Advanced Micro Devices, Inc.

Host PCI Bridge Registers (Device 20, Function 4)

AMD SB600 Register Reference Manual

Proprietary

Page 272

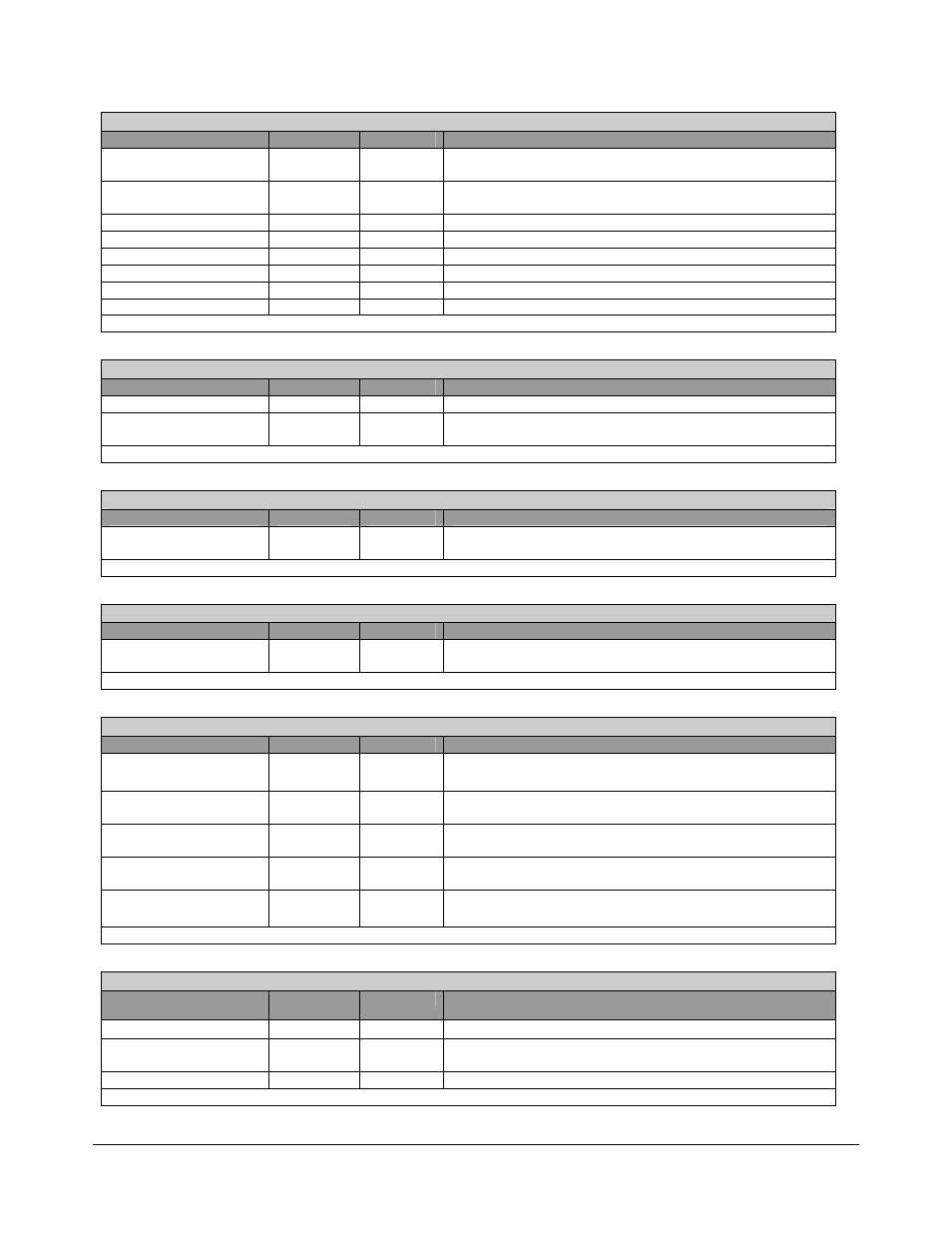

CLKCTRL- RW - 8 bits - [PCI_Reg: 42h]

Field Name

Bits

Default

Description

PCICLKStopEnable

0

0b

33MHz PCICLKs request bit; when ‘1,’ 33 MHz PCI Clocks

are requested to stop.

PCICLKStopStatus 1 0b

Read

only.

33MHz PCICLKs stop status: ‘1’ stopped, ‘0’ running.

PCICLK0Enable

2

1b

33MHz PCICLK0 enable.

PCICLK1Enable

3

1b

33MHz PCICLK1 enable.

PCICLK2Enable

4

1b

33MHz PCICLK2 enable.

PCICLK3Enable

5

1b

33MHz PCICLK3 enable.

P2SControl

6

0b

P_CLK domain to S_CLK domain synch-up disable.

S2PControl

7

0b

S_CLK domain to P_CLK domain synch-up disable.

Clock control register

ARCTRL- RW - 8 bits - [PCI_Reg: 43h]

Field Name

Bits

Default

Description

Reserved 6:0

ffh

Reserved

ArbiterEnable

7

1b

Arbiter enable. ‘0’ disabled to give PCIB the exclusive

ownership of the secondary bus.

Arbiter control register

SMLT_PERF- RW - 16 bits - [PCI_Reg: 44h]

Field Name

Bits

Default

Description

SMLT_Perf

15:0

0000h

Count the total number of a burst being broken into multiple

transactions due to MLT timeout.

Secondary MLT performance register

PCDMA- RW - 8 bits - [PCI_Reg: 48h]

Field Name

Bits

Default

Description

PCDMA Device Enable

A

0

0b

Device enable for request 3. Needs to be enabled when

there is a PCDMA device corresponding to request 3

PCDMA Device Enable

B

1

0b

Device enable for request 4. Heeds to be enabled when

there is a PCDMA device corresponding to request 4

Fast Back to Back Retry

Enable

2

0b

Retry Fast Back to Back transactions on Write buffer full.

Lock Operation Enable

3

1b

When reg0x40[2]=1, this bit should be set to 1 for the proper

operation of the PCI LOCK# function.

Reserved 7:4

00h

Reserved

PCDMA device Enable bits

Additional Priority- Bits RW - 8 bits - [PCI_Reg: 49h]

Field Name

Bits

Default

Description

Reserved 0

0b

PCDMA Priority

1

0b

If enabled includes PCDMA request into high priority list

Reserved 7:2

00h

Reserved

Priority Bits

PMLT_PERF- RW - 16 bits - [PCI_Reg: 46h]

Field Name

Bits

Default

Description

PMLT_Perf

15:0

0000h

Count the total number of a burst being broken into multiple

transactions due to MLT timeout.

Primary MLT performance register