AMD SB600 User Manual

Page 119

©2008 Advanced Micro Devices, Inc.

SMBus Module and ACPI Block (Device 20, Function 0)

AMD SB600 Register Reference Manual

Proprietary

Page 119

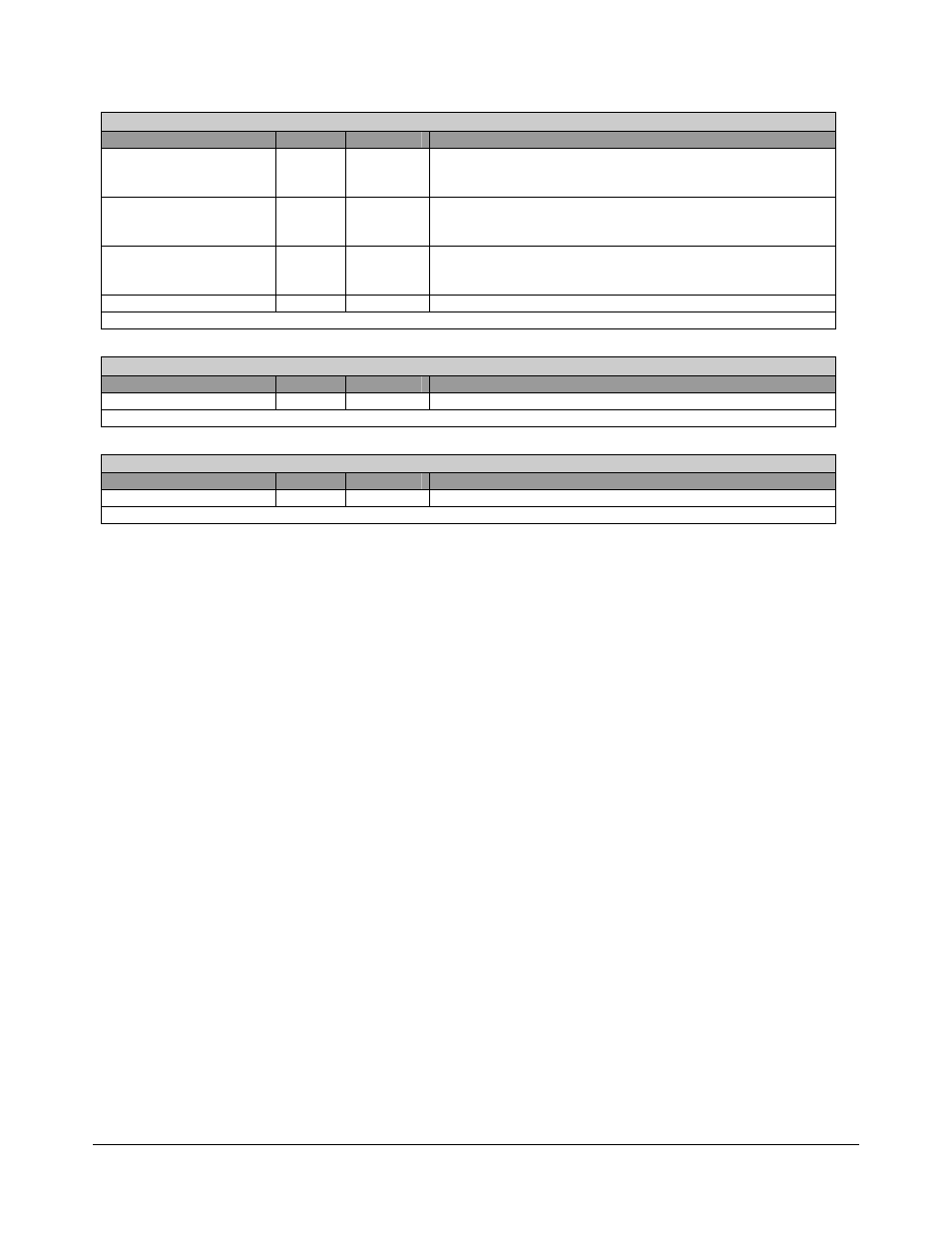

MwaitSts- R - 8 bits - [PCI_Reg: F7h]

Field Name

Bits

Default

Description

Mwait_cpu1_sts

1

0b

Set to 1 by MWAIT with addr[19:18] = Mwait_physical_ID[3:2]

and addr[17:16] = Mwait_logical_ID[1:0]. Cleared by

ADS_after_MWAIT with the same addr[19:16].

Mwait_cpu2_sts

2

0b

Set to 1 by MWAIT with addr[19:18] = Mwait_physical_ID[1:0]

and addr[17:16] = Mwait_logical_ID[3:2]. Cleared by

ADS_after_MWAIT with the same addr[19:16].

Mwait_cpu3_sts

3

0b

Set to 1 by MWAIT with addr[19:18] = Mwait_physical_ID[3:2]

and addr[17:16] = Mwait_logical_ID[3:2]. Cleared by

ADS_after_MWAIT with the same addr[19:16].

Reserved 7:4

0h

MwaitSts register. This register is to be used for P4 dual core system. Usage TBD.

ExtendedAddrPort- RW - 32 bits - [PCI_Reg: F8h]

Field Name

Bits

Default

Description

ExtendedAddrPort 31:0

00h

Address

port for the extended register block

ExtendedAddrPort register..

ExtendedDataPort- RW - 32 bits - [PCI_Reg: FCh]

Field Name

Bits

Default

Description

ExtendedDataPort 31:0

00h

Data

port

for the extended register block

ExtendedDataPort register.