AMD SB600 User Manual

Page 295

©2008 Advanced Micro Devices, Inc.

Real Time Clock (RTC)

AMD SB600 Register Reference Manual

Proprietary

Page 295

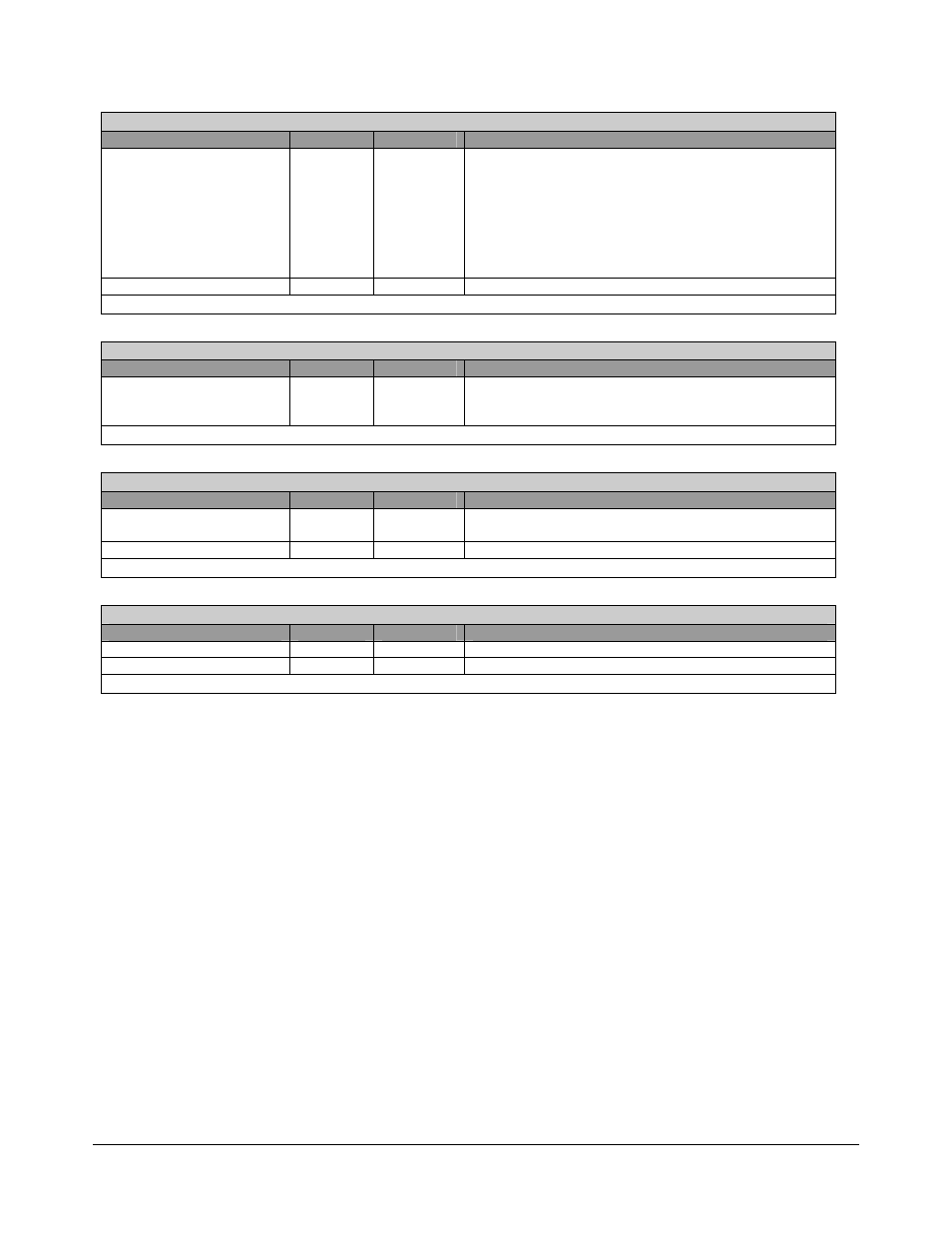

Extended RAM Address Port - RW – 8 bits - [RTC_Reg: 50h]

Field Name

Bits

Default

Description

ExtendedRAMAddr

6:0

00h

Because only 7 address bits are used in port x70, only

lower 128 bytes are accessible through port x71. The

Extended RAM (upper 128 bytes) are physically located

at address 80H to FFH. In order to access these

address, an address offset should be programmed into

this register and access them through Extended

RAMDataPort. (An offset of x80H will automatically add

to this 7-bit address).

Reserved 7

Extended RAM Address Port register: The address port to access Extended RAM.

Extended RAM Data Port - RW – 8 bits - [RTC_Reg: 53h]

Field Name

Bits

Default

Description

Extended RAM Data Port

7:0

xxxxxxxx

There is no physical register corresponding to this data

port but the data port address is used for decoding to

generate appropriate internal control signals.

Extended RAM Data Port register.

RTC Time Clear - RW – 8 bits - [RTC_Reg: 7Eh]

Field Name

Bits

Default

Description

RtcTimeClear

0

0b

Setting this bit will clear the RTC second and RTC time

will stop

Reserved 7:1

0000000b

RTC Time Clear register.

RTC RAM Enable - RW – 8 bits - [RTC_Reg: 7Fh]

Field Name

Bits

Default

Description

RtcRamEnable

0

1b

Setting this bit will enable access to the RTC RAM

Reserved 7:1

0000000b

RTC RAM Enable register.