AMD SB600 User Manual

Page 17

©2008 Advanced Micro Devices, Inc.

SATA Registers (Device 18, Function 0)

AMD SB600 Register Reference Manual

Proprietary

Page 17

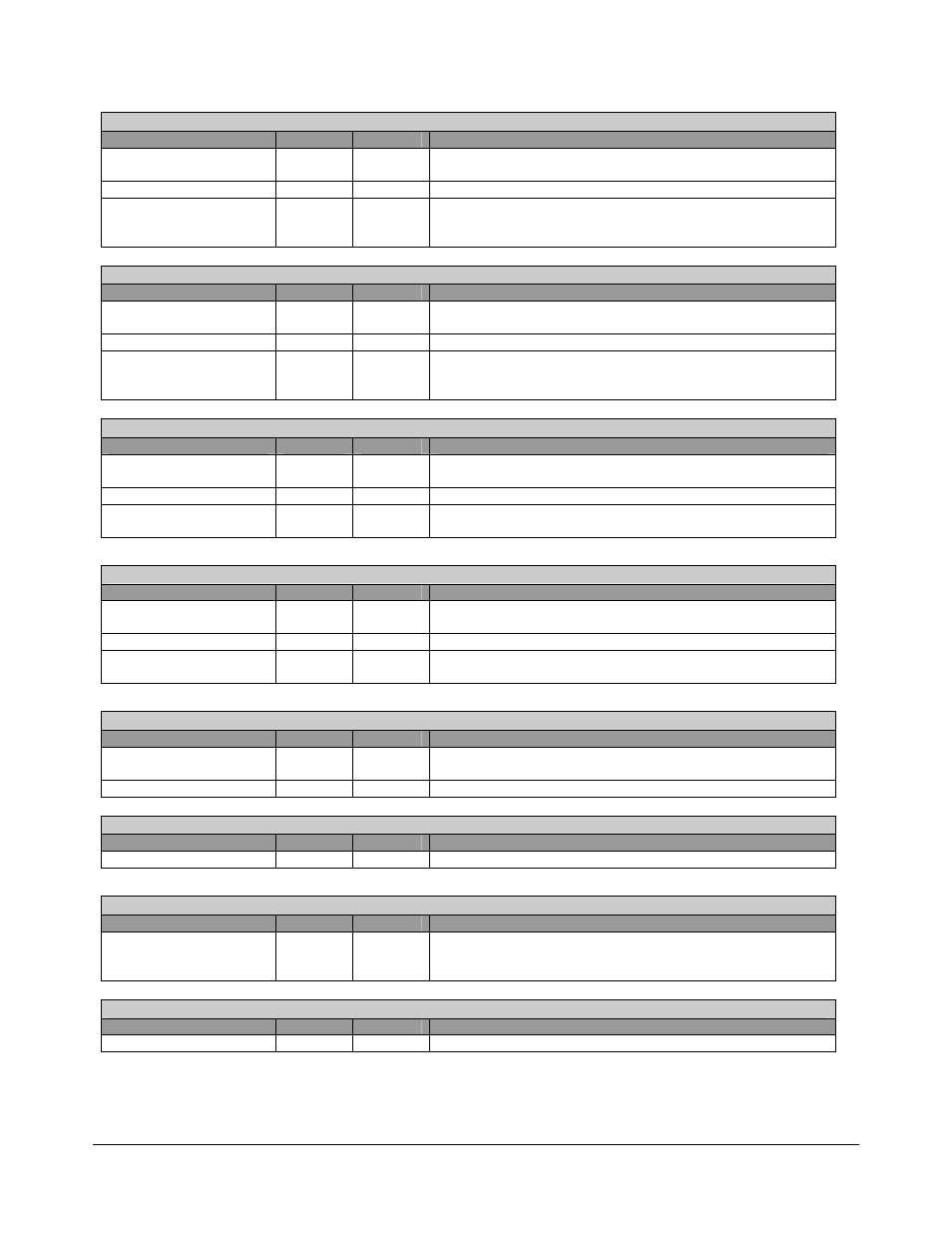

Base Address 2 - RW - 32 bits - [PCI_Reg:18h]

Field Name

Bits

Default

Description

Resource Type Indicator

0

1b

This bit is wired to 1 to indicate that the base address field in

this register maps to I/O space.

Reserved 2:1

Reserved.

Secondary IDE CS0

Base Address

31:3 0000_

0000h

Base Address for Secondary IDE Bus CS0. This register is

used for native mode only. Base Address 2 is not used in

compatibility mode.

Base Address 3 - RW - 32 bits - [PCI_Reg:1Ch]

Field Name

Bits

Default

Description

Resource Type Indicator

0

1b

This bit is wired to 1 to indicate that the base address field in

this register maps to I/O space.

Reserved 1

Reserved.

Secondary IDE CS1

Base Address

31:2 0000_

0000h

Base Address for Secondary IDE Bus CS1. This register is

used for native mode only. Base Address 3 is not used in

compatibility mode.

Bus Master Interface Base Address - RW - 32 bits - [PCI_Reg:20h]

Field Name

Bits

Default

Description

Resource Type Indicator

0

1b

This bit is wired to 1 to indicate that the base address field in

this register maps to I/O space.

Reserved 3:1

Reserved.

Bus Master Interface

Register Base Address

31:4 0000_

000h

Base Address for the Bus Master interface registers, and

corresponds to AD[15:4].

AHCI Base Address - RW - 32 bits - [PCI_Reg:24h]

Field Name

Bits

Default

Description

Resource Type Indicator

0

0b

This bit is wired to 0 to indicate a request for register memory

space.

Reserved 9:1

Reserved.

AHCI Base Address

31:10

000000h

Base address of register memory space. This represents a

memory space for support of 4 ports.

Subsystem ID and Subsystem Vendor ID - RW - 32 bits - [PCI_Reg:2Ch]

Field Name

Bits

Default

Description

Subsystem Vendor ID

15:0

0000h

Subsystem Vendor ID. This can only be written once by the

software.

Subsystem ID

31:16

0000h

Subsystem ID. This can only be written once by the software.

Capabilities Pointer - R - 8 bits - [PCI_Reg:34h]

Field Name

Bits

Default

Description

Capabilities Pointer

7:0

60h

The first pointer of the Capability block

Interrupt Line - RW - 8 bits - [PCI_Reg:3Ch]

Field Name

Bits

Default

Description

Interrupt Line

7:0

00h

Identifies which input on the interrupt controller the function’s

PCI interrupt request pin (as specified in its Interrupt Pin

register) is routed to.

Interrupt Pin - R - 8 bits - [PCI_Reg:3Dh]

Field Name

Bits

Default

Description

Interrupt Pin

7:0

01h

Hard-wired to 01h.