AMD SB600 User Manual

Page 194

©2008 Advanced Micro Devices, Inc.

IDE Controller (Device 20, Function 1)

AMD SB600 Register Reference Manual

Proprietary

Page 194

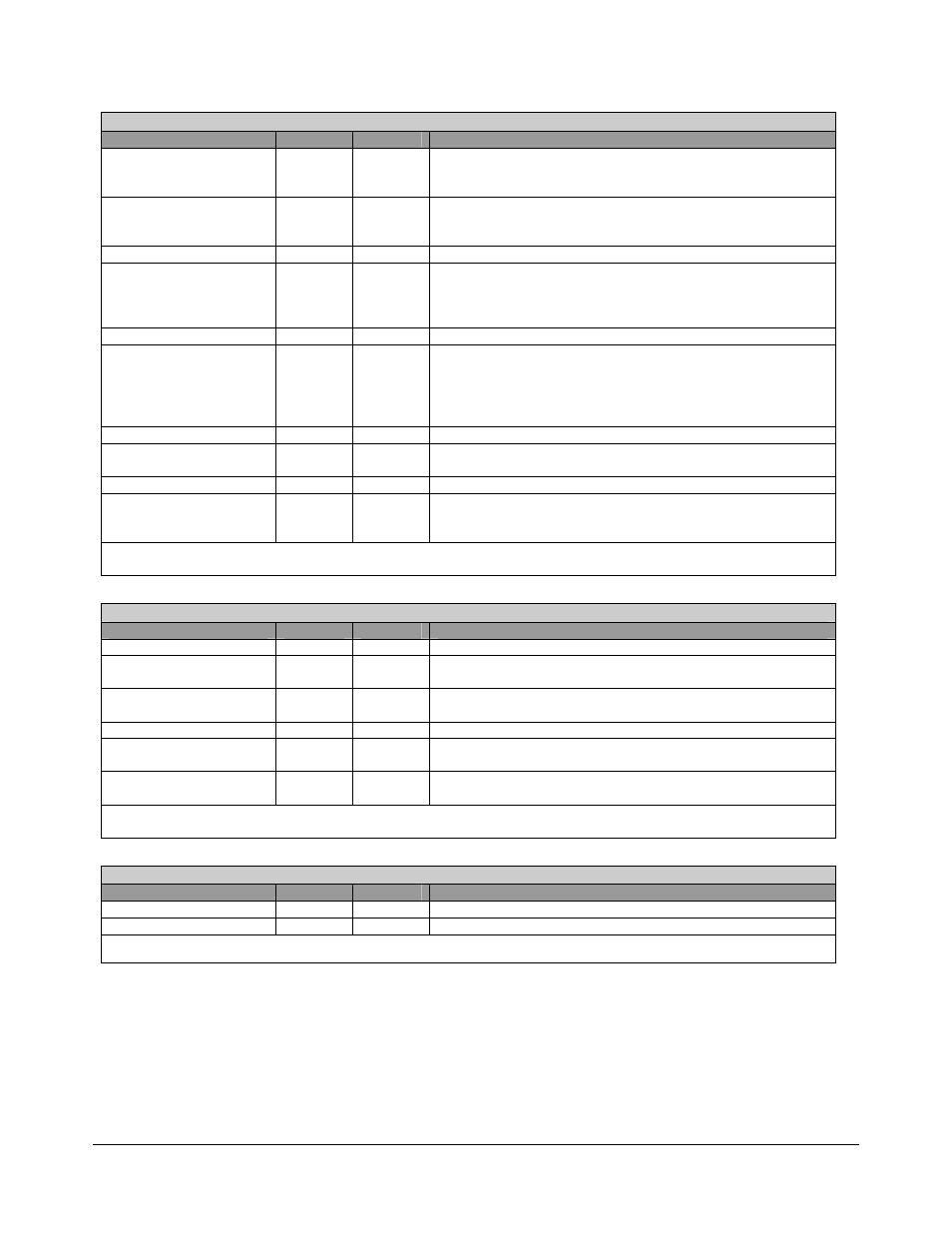

IDE Internal Control - RW- 16 bits - [PCI_Reg:62h]

Field Name

Bits

Default

Description

IDE Internal PCI master

request selection

0

0b

Select number of delay cycles on internal PCI master request

0: delay two PCI cycles

1: delay three PCI cycles

IDE PCI request control

1

0b

Control PCI request deassertion timing at PCI retry cycle.

0: allows IDE’s PCI request to be deasserted one cycle early.

1: PCI request will be deasserted one cycle late.

Reserved

5:2

0h

Reserved. Always read as 0’s

IDE Fast sampling

Enable

6

1

b

Enable fast sampling on IORDY (DDMARDY#) port

0: Use regular IDE clock to sample

1: Use either (50/66MHz) sampling IORDY (DDMARDY#) port

at ultra DMA mode

Reserved 7

0b

Reserved.

Explicit/Implicit prefetch

Switch

8

0b

Control implicit or explicit prefetch function

0: Explicit prefetch is enabled

1: Implicit prefetch is enabled

Recommendation is to have it reset to 0 for better bus

efficiency

Reserved 12:9

0h

Reserved

MSI capability visible

control

13

0b

When this bit is set MSI capability will be visible.

Reserved 14

0b

Reserved

MSI_MME[0] hidden

control bit

15

0b

Control Multiple/Single Message Enable

0: Only 1 message allocated

1: 2 messages allocated

IDE Internal Control Register: This register can enable internal PCI request timing and different IDE arbitration

schemes.

IDE Misc. Control - RW- 32 bits - [PCI_Reg:64h]

Field Name

Bits

Default

Description

Reserved 0

0b

Reserved.

IDE Internal Logic Reset

1

0b

IDE internal reset. This reset follows IDE PLL reset. Software

control the duration between both resets.

Primary Channel Tri-

state Mode

2

0b

Primary channel tri-state mode if it is set to 1.

Reserved

3

0b

Reserved. Always read as 0’s.

Preliminary Buffer

Threshold Control

6:4

001b

Programmable threshold control for preliminary buffer.

Reserved 31:7

00E0258

h

Reserved. Do not use

IDE Misc. Control Register: This register specifies IDE tri-state channel enable, and preliminary buffer threshold

control.

IDE MSI Programmable Weight - RW- 8 bits - [PCI_Reg:68h]

Field Name

Bits

Default

Description

MSI Interrupt Weight

5:0

01h

MSI programmable interrupt weight.

Reserved

7:6

0h

Reserved. Always wired as 0’s.

IDE MSI Programmable Weight Register: This register specifies MSI weight.