AMD SB600 User Manual

Page 162

©2008 Advanced Micro Devices, Inc.

SMBus Module and ACPI Block (Device 20, Function 0)

AMD SB600 Register Reference Manual

Proprietary

Page 162

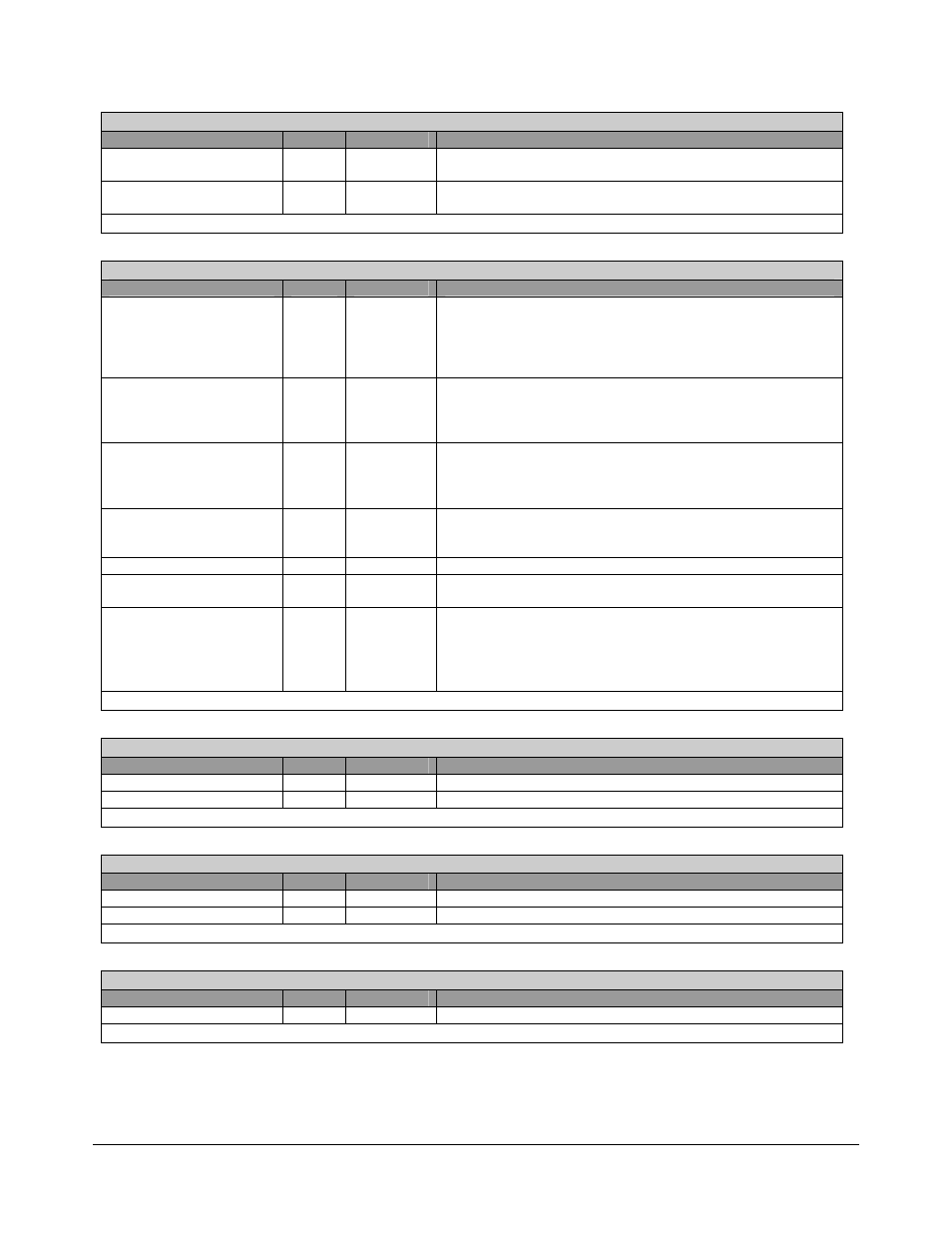

MiscEnable67 – RW – 8 bits – [PM_Reg:67h]

Field Name

Bits

Default

Description

TempPolarity

6:5

00b

Temperature polarity control for THRMTRIP and TALERT

respectively. 0: active low; 1; active high

DlySlpEn

7

0b

Set to 1 to delay recognition of STPGNT# until there is no

pending read in AB

MiscEnable67 register

MiscEnable68 – RW – 8 bits – [PM_Reg:68h]

Field Name

Bits

Default

Description

NicePBE

0

0b

When set, the CPU ‘s assertion of PBE# during C state will

cause SB to break out from C state gracefully; i.e., it will finish

the C state entry sequence first before it will revert back to C0.

If this bit is not set, it will break out from C state abruptly. It is

recommended to set this bit.

MaskCState

1

0b

(Use this only for the P4 system. Leave it 0 for the K8 system).

If this bit is set, the pending break event will prevent the SB

from entering C state. The LVL read will be completed with no

effect.

MaskApicEn

2

0b

If set, the APIC interrupt will be deferred until the first ACPI

access when the system resumes from S state. For K8 CPU

additionally A20M# IGNNE# INTR NMI INIT# will be deferred

the same way, but SMI# will not be deferred.

THRMTRIP_Enable

3

1b

When set, GEVENT2 becomes THRMTRIP function. When

THRMTRIP pin is low and PM 55h, bit 0 is set, hardware will

switch the system to S5 automatically.

MaskRtcClkOut

4

0b

If set, RtcClkOut will stop toggling.

LLB_Enable

5

0b

If set, LLB function is enabled, system won’t wakeup from

ACPI S state until LLB# is de-asserted.

AcpiThrotPeriod

7:6

00b

Selects the software clock throttling period

00: 15

µs

01: 30

µs

10: 244

µs

11: Reserved

MiscEnable68 register

WatchDogTimerControl – RW – 8 bits – [PM_Reg:69h]

Field Name

Bits

Default

Description

WatchDogTimerDisable

0

1b

When set, watchdog timer will be disabled

Reserved 7:1

00h

WatchDogTimerControl register

WatchDogTimerBase0 – RW – 8 bits – [PM_Reg:6Ch]

Field Name

Bits

Default

Description

Reserved 2:0

000b

WatchDogTimerBase0

7:3

00000b

WatchDogTimer Base address [7:3]

WatchDogTimerBase0 register

WatchDogTimerBase1 – RW – 8 bits – [PM_Reg:6Dh]

Field Name

Bits

Default

Description

WatchDogTimerBase1 7:0 00h

WatchDogTimer Base address [15:8]

WatchDogTimerBase1 register