AMD SB600 User Manual

Page 293

©2008 Advanced Micro Devices, Inc.

Real Time Clock (RTC)

AMD SB600 Register Reference Manual

Proprietary

Page 293

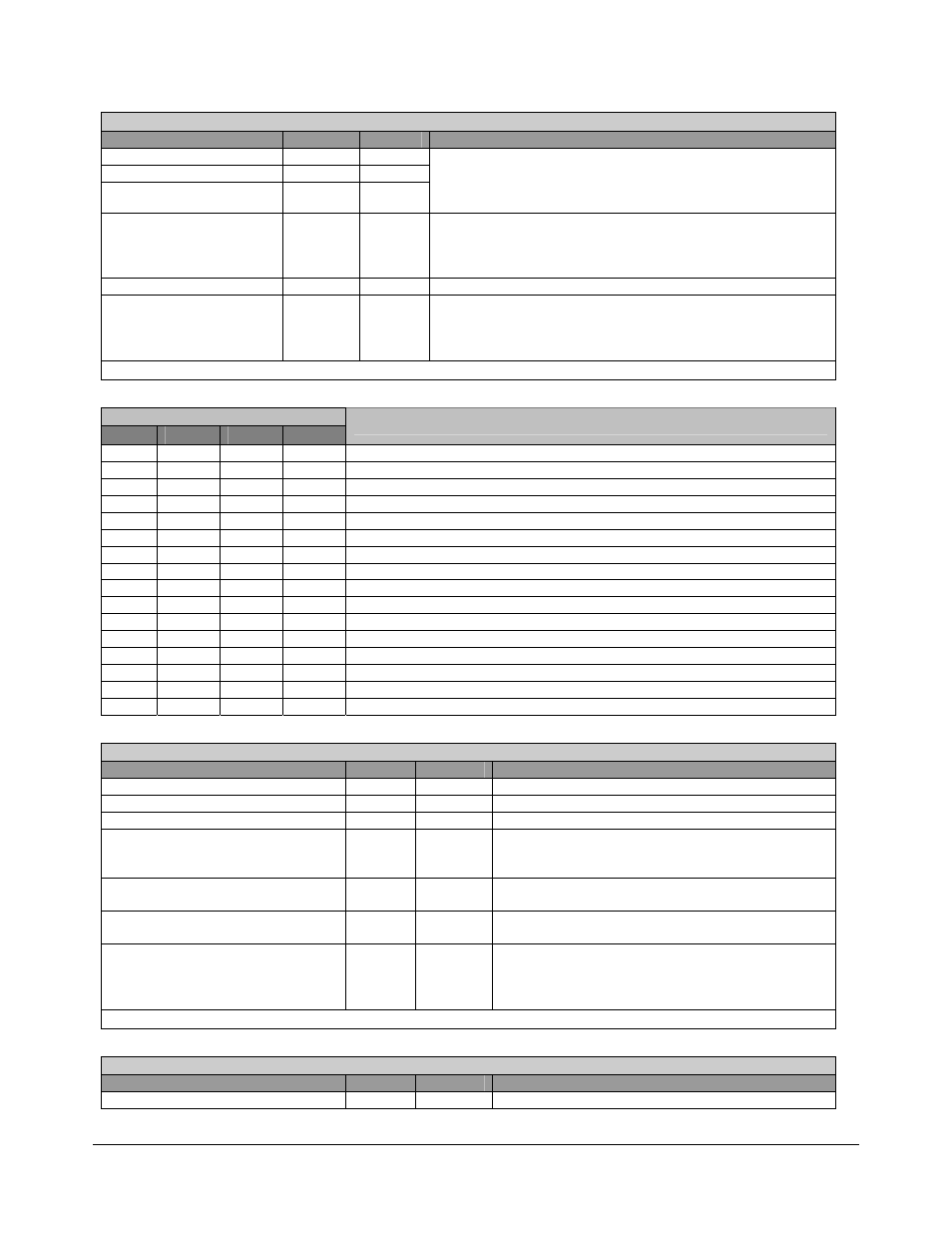

Register A - RW – 8 bits - [RTC_Reg: 0Ah]

Field Name

Bits

Default

Description

Rate Selection(RS1)

1

0b

Rate Selection(RS2)

2

0b

Rate Selection(RS3)

3

0b

15-stage frequency divider or disable the divider output (flat

output signal). The tap selected can be used to generate a

periodic interrupt. See the following table for frequency

selection.

Bank Selection(DV0)

4

0b

DV0 = 0 selects Bank 0; DV0 = 1 selects Bank 1. The SB600,

it has an alternate way to access the RAM without the use of

bank select bit. Port 72/73 can be used as the index to access

the full 256 bytes of RAM directly.

Reserved 6:5

Update In Progress(UIP)

7

0b

If SET bit = 1, UIP is cleared.

If UIP = 1, the update transfer will soon occur.

If UIP = 0, the update transfer will not occur for at least 244us.

[Read-only]

Register A: Control register

Rate Selection Bits

RS3

RS2

RS1

RS0

Tap Frequency(Interrupt Rate)

0 0 0 0

Flat

Signal(None)

0

0

0

1

256 Hz (3.90625 ms)

0

0

1

0

128 Hz (7.8125 ms)

0

0

1

1

8.192 kHz (122.070 us)

0

1

0

0

4.096 kHz (244.141 us)

0

1

0

1

2.048 kHz (488.281 us)

0

1

1

0

1.024 kHz (976.5625 us)

0

1

1

1

512 Hz (1.953125 ms)

1

0

0

0

256 Hz (3.90625 ms)

1

0

0

1

128 Hz (7.8125 ms)

1 0 1 0

64

Hz

(15.625

ms)

1

0

1

1

32 Hz (31.25 ms)

1

1

0

0

16 Hz (62.5 ms)

1

1

0

1

8 Hz (125 ms)

1

1

1

0

4 Hz (250 ms)

1

1

1

1

2 Hz (500 ms)

Register B - RW – 8 bits - [RTC_Reg: 0Bh]

Field Name

Bits

Default

Description

Reserved 0

0b

HourMode

1

0b

Hour mode; 0 = 12 hour mode; 1 = 24 hour mode

Reserved 3:2

00

Update Ended Interrupt Enable(UIE)

4

0b

UIE enables the Update End Flag (UF) bit in

Register C to assert IRQ. If SET bit = 1, UIE is

cleared.

Alarm Interrupt Enable (AIE)

5

0b

AIE enables the Alarm Flag (AF) bit in Register C to

assert IRQ.

Periodic Interrupt Enable (PIE)

6

0b

PIE enables the Periodic Interrupt Flag (PF) bit in

Register C to assert IRQ.

Set new time (SET)

7

0b

If SET bit = 1, no internal updating for Time

Registers is allowed.

If SET bit = 0, the Time Registers are updated every

second.

Register B: Control register

Register C - R – 8 bits - [RTC_Reg: 0Ch]

Field Name

Bits

Default

Description

Reserved 3:0

0h