AMD SB600 User Manual

Page 219

©2008 Advanced Micro Devices, Inc.

AC ’97 Controller Functional Descriptions

AMD SB600 Register Reference Manual

Proprietary

Page 219

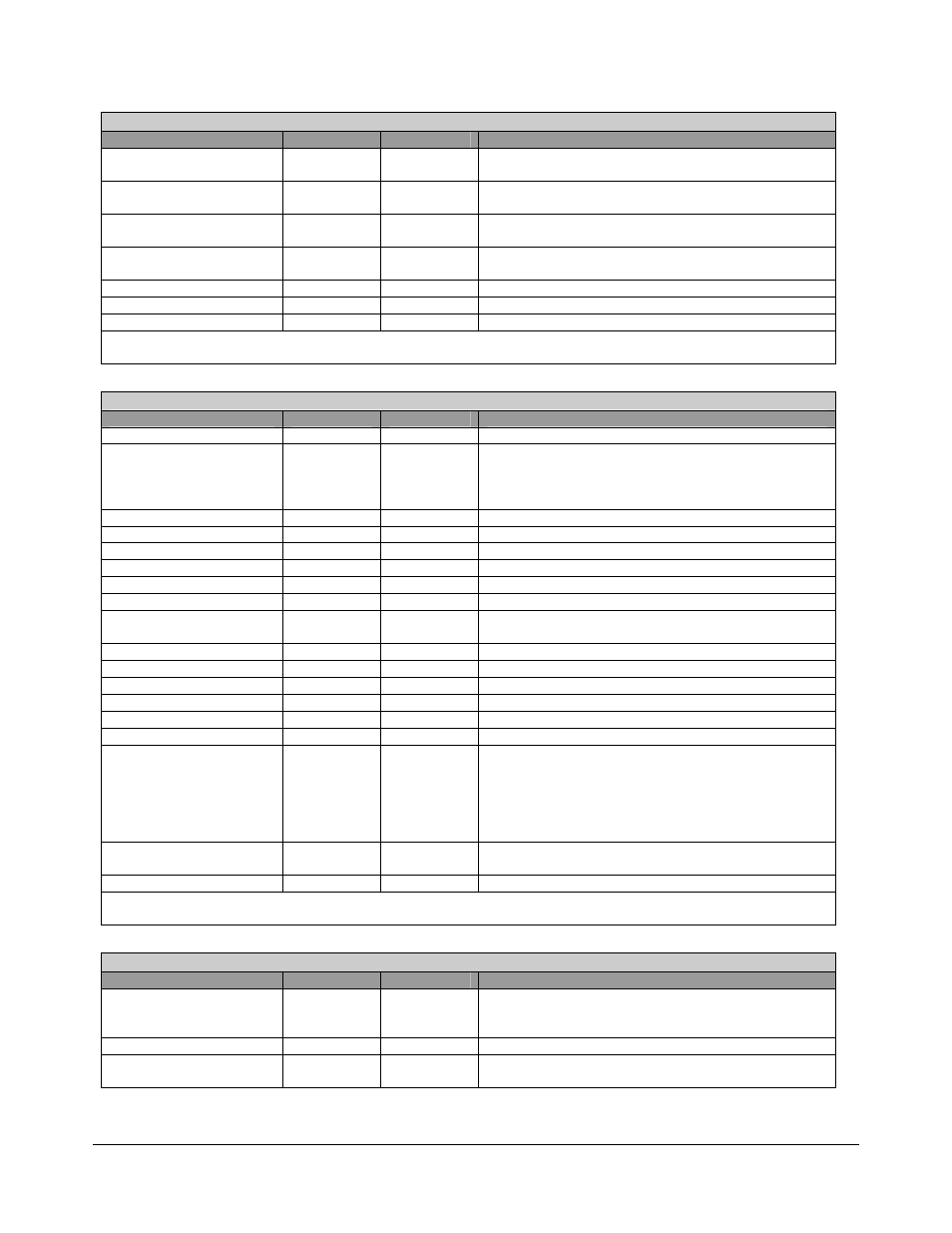

Interrupt - RW - 32 bits - [MEM_Reg: 00h]

Field Name

Bits

Default

Description

Phy Addr mismatch

9

0b

There is mismatch between in Phy and out Phy

address values

Codec0 Not Ready

10

0b

The Ac97_Phy registers in the master Ac97 are not

ready for normal operation

Codec1 Not Ready

11

0b

The Ac97_Phy registers in the 1

st

slave Ac97 are not

ready for normal operation

Codec2 Not Ready

12

0b

The Ac97_Phy registers in the 2

nd

slave Ac97 are not

ready for normal operation

New Frame Starts

13

0b

Signal when new frame starts

Gpio in Data Intr.

14

0b

Got Gpio data from Codec

Reserved 31:15

00000h

Interrupt Source Register: Each bit in this register expresses an error flag. "1" indicates the error. Driver can read

status or clear by writing “1”. Writing 0 to bit doesn't change its value.

Interrupt Enable - RW - 32 bits - [MEM_Reg: 04h]

Field Name

Bits

Default

Description

in DMA Overflow en

0

0b

Enables Input Channel overflow interrupt.

Status enable

1

0b

1 – When an input or output modem DT data block is

finished, status will be updated in either DT memory or

in reg0x00 (depending on reg0x08[5]).

0 - Don’t update status

out DMA1 Underflow en

2

0b

Enables out DMA3 underflow interrupt.

Reserved 3

0b

out DMA2 Underflow en

4

0b

Enables out DMA3 underflow interrupt.

Reserved 5

0b

out DMA3 Underflow en

6

0b

Enables out DMA3 underflow interrupt.

Reserved 7

0b

Phy in Intr. En

8

0b

Enables "Got Physical register data from Codec"

interrupt.

Phy_addr_mismatch_en 9

0b

Enables

Physical address in/out mismatch interrupt

Codec0_not_ready en

10

0b

Enables Codec0 Not Ready interrupt

Codec1_not_ready en

11

0b

Enables Codec1 Not Ready interrupt

Codec2_not_ready en

12

0b

Enables Codec2_not_ready interrupt

New_Frame_start enable

13

0b

Enables new frame start interrupt

Gpio in Data Intr. En

14

0b

Enables "Got Gpio data from Codec" interrupt

Gpio in Data Intr. Diff En

15

0b

This bit is effective only when “Gpio in Data Intr En” bit

is asserted.

0 – Gpio interrupt happens whenever valid GPIO data

come in

1 – Gpio interrupt happens only when valid GPIO data

change in different frames.

Set Bus Busy Modem

16

0b

Modem is running (write only). Set/cleared by

software.

Reserved 31:17

0000h

Interrupt Enable Register: If a bit in this register is set to “1”, then the corresponding interrupt is enabled. Default --

all disabled.

Modem Command - RW - 32 bits - [MEM_Reg: 08h]

Field Name

Bits

Default

Description

Power down

0

0b

When this bit is set, the INTA# will be only set when

any of the SDATA_IN is '1'. Should be used for

catching of PME# event.

Modem receive enable

1

0b

Enables receiving of modem data from AC link.

Modem send out through

DMA1 enable

2

0b

Enables sending of modem data to slot 5 on AC link

using out DMA1