AMD SB600 User Manual

Page 71

©2008 Advanced Micro Devices, Inc.

OCHI USB 1.1 and EHCI USB 2.0 Controllers

AMD SB600 Register Reference Manual

Proprietary

Page 71

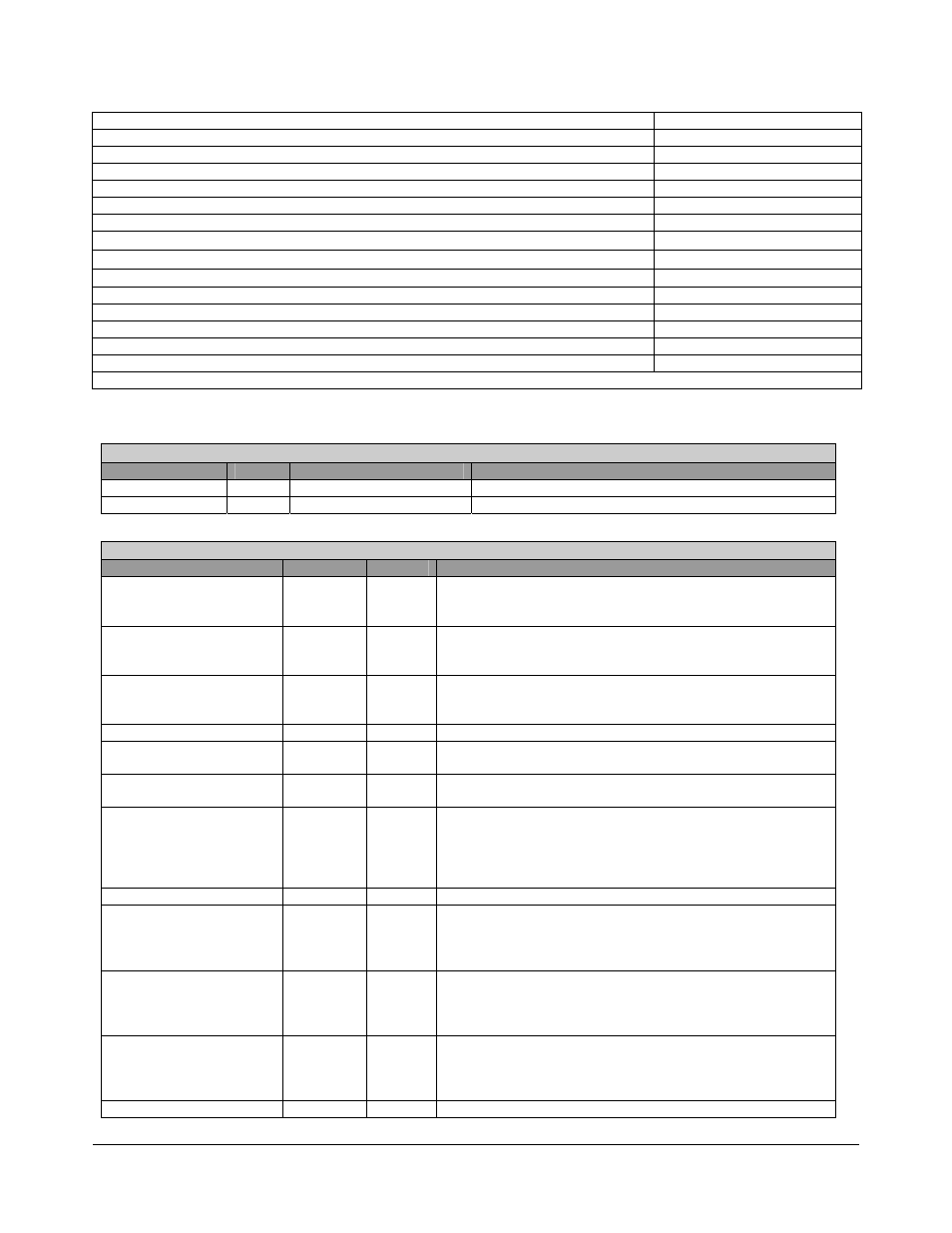

Base Address – BAR_EHCI

10h

Subsystem ID / Subsystem Vendor ID

2Ch

Capability Pointer

34h

Interrupt Line

3Ch

EHCI Misc Control

50h

Serial Bus Release Number – SBRN

60h

Frame Length Adjustment – FLADJ

61h

PME Control

C0h

PME Data / Status

C4h

MSI Control

D0h

MSI Address

D4h

MSI Data

D8h

EHCI Debug Port Support

E4h

USB Legacy Support Extended Capability – USBLEGSUP

EECP+0h

1

USB Legacy Support Control/Status - USBLEGCTLSTS

EECP+4h

1

1

The EECP field is in the read-only HCCPARAMS register [MEM_Reg: 08h] with the value of A0h.

DEVICE / VENDOR ID – R - 32 bits - [PCI_Reg : 00h]

Field Name

Bits

Default

Description

VEND_ID 15:0 1002h Vendor

ID

DEV_ID

31:16

Function 5: 4386h

Device ID

Command – RW - 16 bits - [PCI_Reg : 04h]

Field Name

Bits

Default

Description

IO Space Accesses

0

0b

A value of 0 disables the device response.

A value of 1 allows the device to respond to I/O Space

accesses.

Memory Space Accesses

1

0b

A value of 0 disables the device response.

A value of 1 allows the device to respond to Memory Space

accesses.

Bus Master

2

0b

A value of 0 disables the device from generating PCI

accesses.

A value of 1 allows the device to behave as a bus master.

Special Cycle

3

0b

Hard-wired to 0, indicating no Special Cycle support.

Memory Write and

Invalidate Command

4

0b

When it is 0, Memory Write must be used.

When it is 1, masters may generate the command.

VGA Palette Register

Accesses

5

0b

Hard-wired to 0, indicating the device should treat palette

write accesses like all other accesses.

Parity Enable

6

0b

When it is 1, the device must take its normal action when a

parity error is detected.

When it is 0, the device sets its Detected Parity Error status

bit (bit 15 in the Status register) when an error is detected,

but does not assert PERR# and continues normal operation.

Reserved

7

0b

Hard-wired to 0 per PCI2.3 spec.

SERR# Enable

8

0b

A value of 0 disables the SERR# driver.

A value of 1 enables the SERR# driver.

Address parity errors are reported only if this bit and bit [6]

are 1.

Fast Back-to-Back Enable

9

0b

A value of 0 means fast back-to-back transactions to the

same agent only are allowed.

A value of 1 means the master is allowed to generate fast

back-to-back transactions to different agents.

Interrupt Disable

10

0b

A value of 0 enables the assertion of the device/function’s

INTx# signal.

A value of 1 disables the assertion of the device/function’s

INTx# signal.

Reserved 15:11

Reserved