AMD SB600 User Manual

Page 138

©2008 Advanced Micro Devices, Inc.

SMBus Module and ACPI Block (Device 20, Function 0)

AMD SB600 Register Reference Manual

Proprietary

Page 138

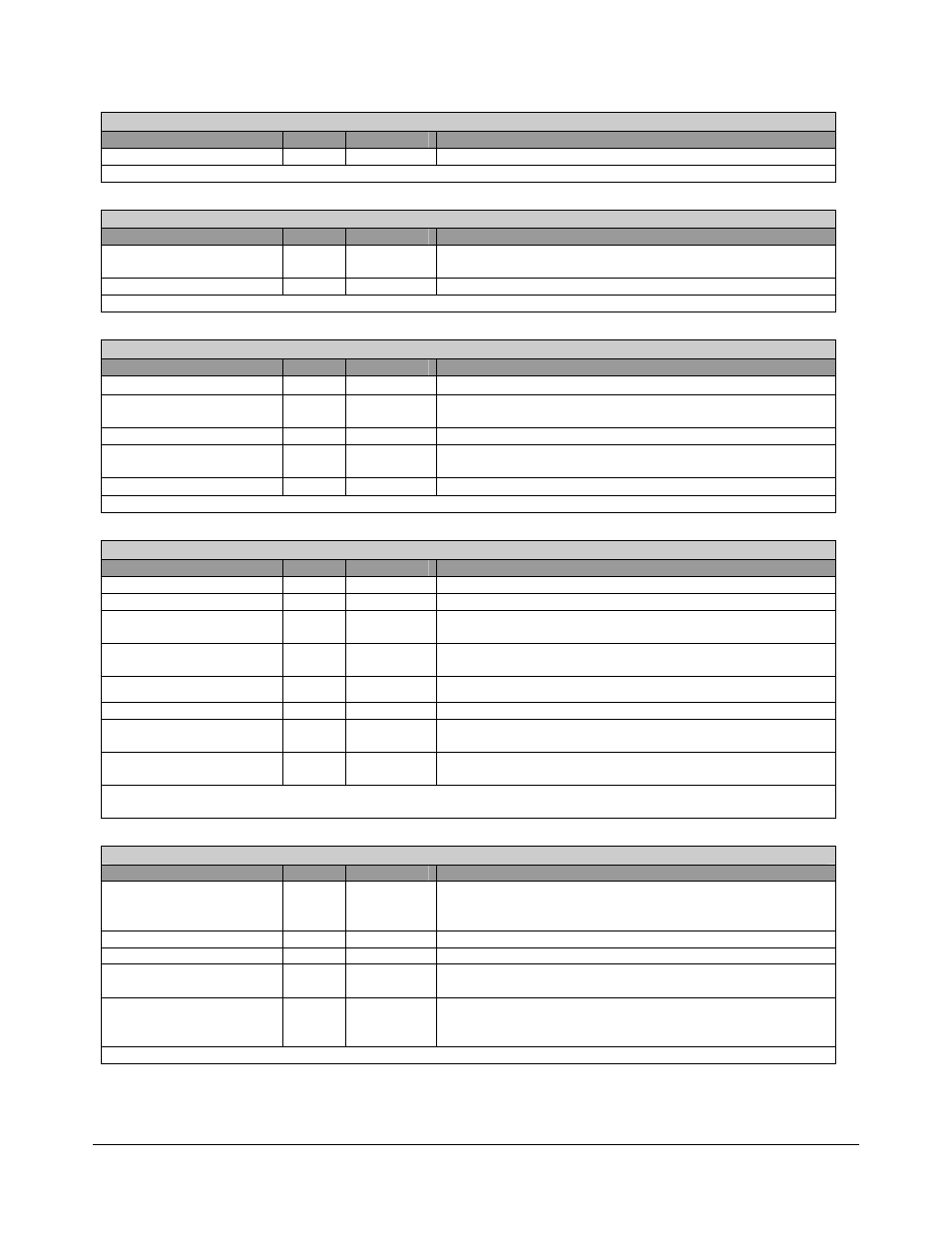

IdRegister - R – 8 bits - [IO_Reg: 00h]

Field Name

Bits

Default

Description

IdRegister 7:0

00h

IdRegister register

TempStatus - R – 8 bits - [IO_Reg: 02h]

Field Name

Bits

Default

Description

TALERT 0

-

Logical

status

of TALERT/GPIO64 input.

Read will clear this bit.

Reserved 7:1

00h

TempStatus register

TempInterrupt - RW – 8 bits - [IO_Reg: 03h]

Field Name

Bits

Default

Description

Reserved 0

0b

TempSmiEnable

1

0b

1 - Generate SMI# upon TALERT

0 - Do not generate SMI# upon TALERT

Reserved 2

0b

ScratchBit

3

0b

This placebo bit has no function, but it may be used for

software status

Reserved 7:4

0h

TempInterrupt register

I2CControl - RW – 8 bits - [IO_Reg: 12h]

Field Name

Bits

Default

Description

Gpoc0Status

0

-

Gpoc0 status. [Read-only]

Gpoc1Status

1

-

Gpoc1 status. [Read-only]

Gpoc0_OE_

2

1b

1 - Gpoc0 is tristate

0 - Gpoc0 is asserted low

Gpoc1_OE_

3

1b

1 - Gpoc1 is tristate

0 - Gpoc1 is asserted low

Gpoc2Status

4

-

Gpoc2 status. [Read-only]

Gpoc3Status

5

-

Gpoc3 status. [Read-only]

Gpoc2_OE_

6

1b

1 - Gpoc2 is tristate

0 - Gpoc2 is output enabled

Gpoc3_OE_

7

1b

1 – Gpoc3 is tristate

0 – Gpoc3 is output enabled

I2CControl register: Writing to this register controls the output of the four Gpoc outputs (GPOC[3:0]_OE) and

reading returns the status of these pins.

Index13– 8 bits - [IO_Reg: 13h]

Field Name

Bits

Default

Description

GPIO64En

0

0b

GPIO64 output enable

1 = Enable

0 = Tristate

GPIO64OUT

1

0b

GPIO64 output data

Gpoc[3:2]OUT

3:2

00b

Gpoc[3:2] output data

ScratchBit

5:4

00b

Placebo bit, has no function but may be used for software

status

GpmPortSel 7:6

00b

00-Read

port

01-Output enable

10-Output port

Index13 misc control register